Other Parts Discussed in Thread: OMAP-L137

Hi,all:

firstly,this is part of the program of my project:

void PSC0_lPSC_enable(Uint8 PD, Uint8 LPSC_num)

{

*(Uint32*) (PSC0_MDCTL+4*LPSC_num) = (*(Uint32*) (PSC0_MDCTL+4*LPSC_num) & 0xFFFFFFE0) | 0x0003;

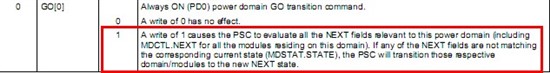

PSC0_PTCMD = 0x1<<PD; //GO[0]=0x1

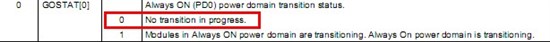

while( (PSC0_PTSTAT & (0x1<<PD) ) !=0) ; /*Wait for power state transition to finish;GOSTAT[0]=0*/

while( (*(Uint32*)(PSC0_MDSTAT+4 * LPSC_num) & 0x1F) !=0x3);

}

void initpsc( void)

{

// PSC0

PSC0_lPSC_enable(0, 0);

PSC0_lPSC_enable(0, 1);

PSC0_lPSC_enable(0, 2);

PSC0_lPSC_enable(0, 3); // EMIFA

PSC0_lPSC_enable(0, 4);

PSC0_lPSC_enable(0, 5);

PSC0_lPSC_enable(0, 6);

PSC0_lPSC_enable(0, 8);

PSC0_lPSC_enable(0, 9);

PSC0_lPSC_enable(0, 10);

PSC0_lPSC_enable(0, 11);

PSC0_lPSC_enable(0, 12);

PSC0_lPSC_enable(0, 13);

// PSC1

PSC1_lPSC_enable(0, 1);

PSC1_lPSC_enable(0, 2);

PSC1_lPSC_enable(0, 3);

PSC1_lPSC_enable(0, 4);

PSC1_lPSC_enable(0, 5);

PSC1_lPSC_enable(0, 6); // EMIFB

PSC1_lPSC_enable(0, 7);

PSC1_lPSC_enable(0, 8);

PSC1_lPSC_enable(0, 9);

PSC1_lPSC_enable(0, 10);

PSC1_lPSC_enable(0, 11);

PSC1_lPSC_enable(0, 12);

PSC1_lPSC_enable(0, 13);

PSC1_lPSC_enable(0, 16);

PSC1_lPSC_enable(0, 17);

PSC1_lPSC_enable(0, 20);

PSC1_lPSC_enable(0, 21);

PSC1_lPSC_enable(0, 24);

PSC1_lPSC_enable(0, 25);

PSC1_lPSC_enable(0, 26);

PSC1_lPSC_enable(0, 31);

}

the question is :

why the program stop at :while( (PSC0_PTSTAT & (0x1<<PD) ) !=0) ; all the time . This is an infinite loop.

thanks

--yefei