Other Parts Discussed in Thread: SYSCONFIG

Hi,

I have question about ELM registers for AM5726.

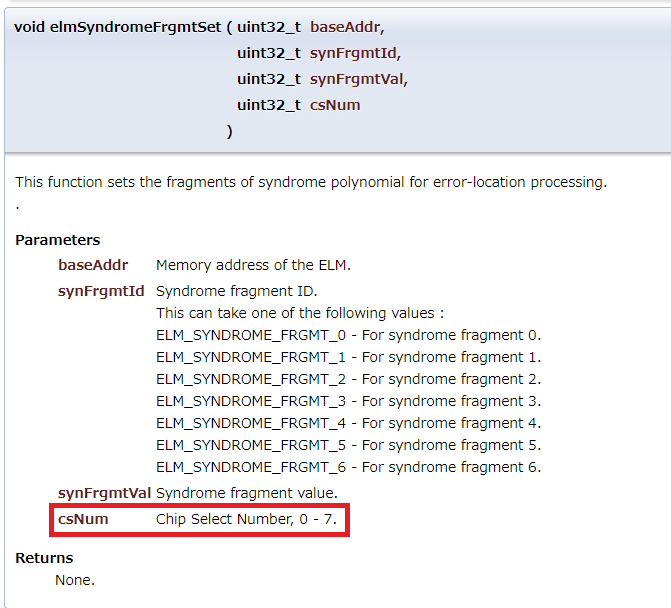

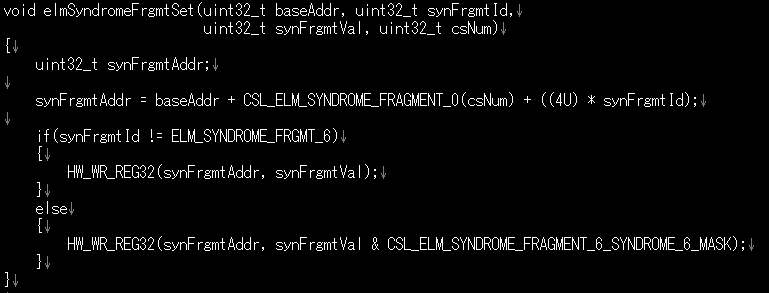

In TRM, "i" is written in the following register and bit field. Does this indicate the chip select number of the GPMC to which the NAND is connected?

ELM_SYNDROME_FRAGMENT_*_i

ELM_IRQENABLE.LOCATION_MASK_i bit

ELM_IRQSTATUS.LOC_VALID_i bit

ELM_LOCATION_STATUS_i

ELM_ERROR_LOCATION_*_i

For example, if I want to connect NAND memory to the chip select number 2 of GPMC, should I use the following registers?

ELM_SYNDROME_FRAGMENT_*_2

ELM_IRQENABLE.LOCATION_MASK_2 bit

ELM_IRQSTATUS.LOC_VALID_2 bit

ELM_LOCATION_STATUS_2

ELM_ERROR_LOCATION_*_2

Best regards,

H.U