Hi,

I'm using AM3356 to connect to EMAC chip LAN8720A.

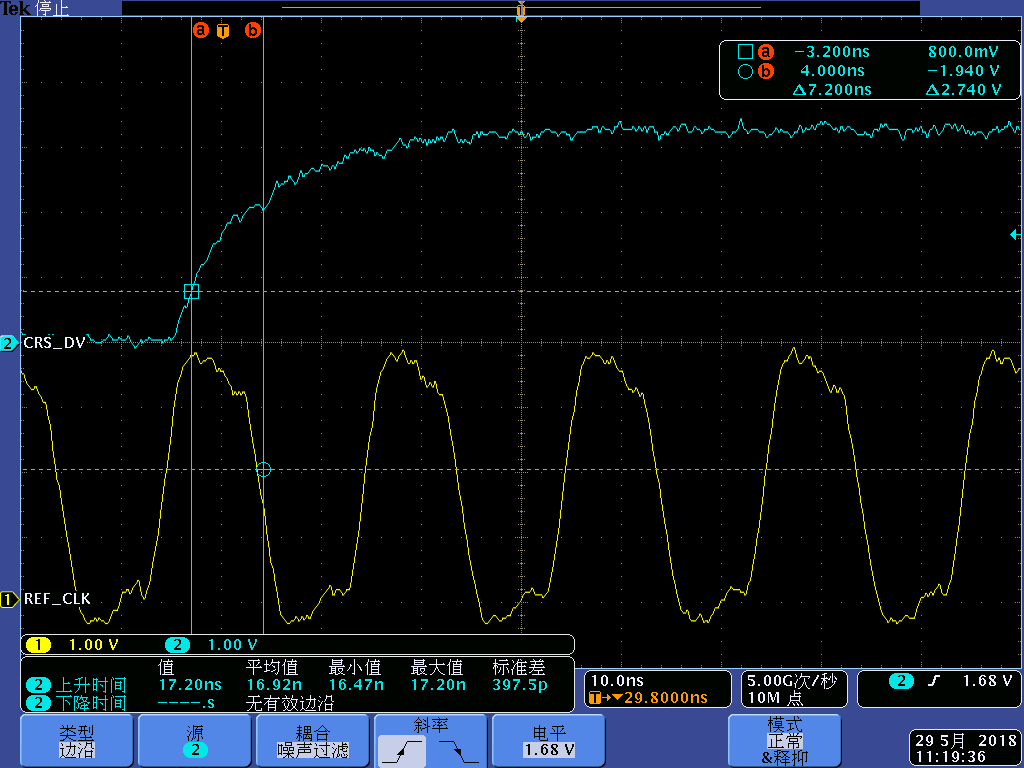

LAN8720 toggle its RXD, CRS_DV and RXER at the rising edge of its 50MHz clock output REFCLK, the Max Tco is 5ns.

While AM3356 also latches the RXD, CRS_DV and RXER at the rising ege of REFCLK input according to Figure 7-11 in the datasheet, it requires setup of 4ns and hold of 2ns.

When connecting LAN8720 signals directly to AM3356 without addional timing adjustment component, the RXD, CRS_DV and RXER's setup and hold time may not be met for AM3356, or may not have enought margin.

So is there one configuration resister in AM3356 that I can set the processor to latch RXD, CRS_DV and RXER at the falling edge of the REFCLK to increase the setup time and hold time margin?

Thanks,

Peng,