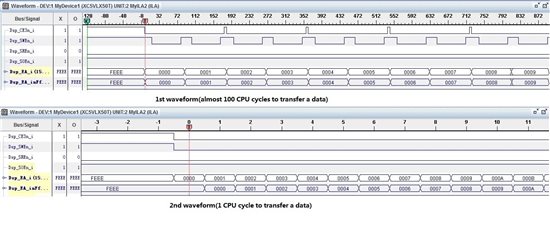

Hi, everyone. In my board, DSP(6455) transfers data from L2 RAM to external memory with EDMA3. After power up, I found DSP run normally(EDMA3 has low efficiency, it uses almost 80 CPU cycles to transfer a data) with its first loaded program. But if the program reloaded(.out file not changed) or restarted, DSP could run normally(EDMA3 transfer a data in one CPU cycle). what is the reason?

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.