Other Parts Discussed in Thread: TMDXICE110, UNIFLASH

Tool/software: TI-RTOS

Hi,

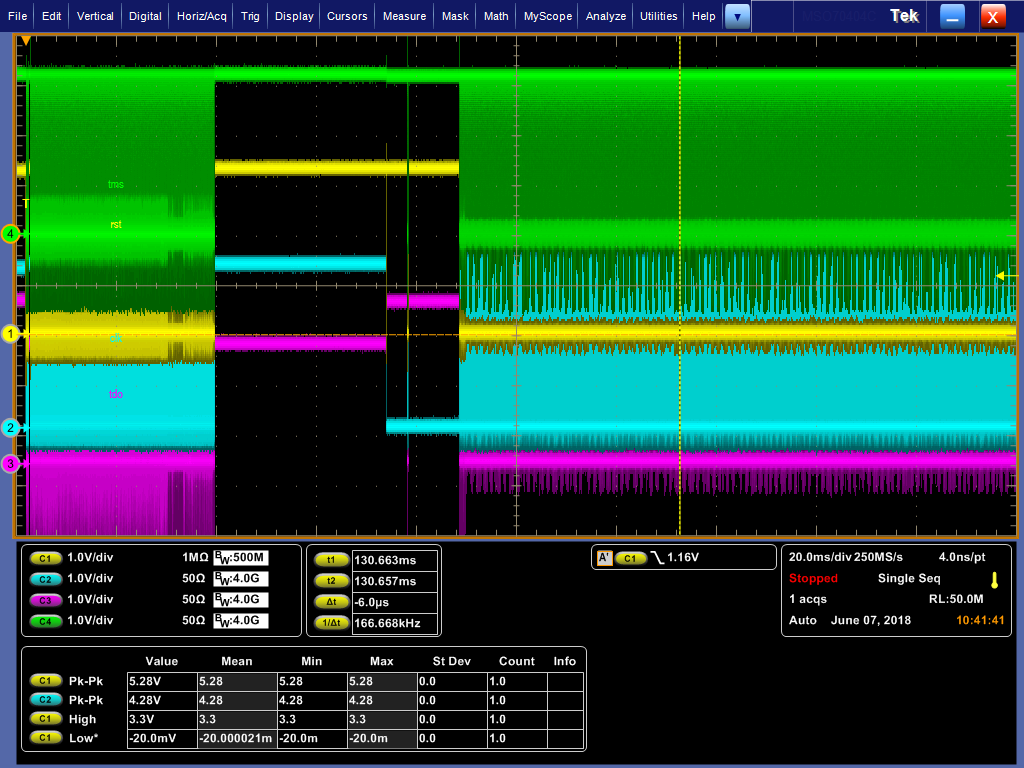

booting up the amic takes really long, like 10 seconds.

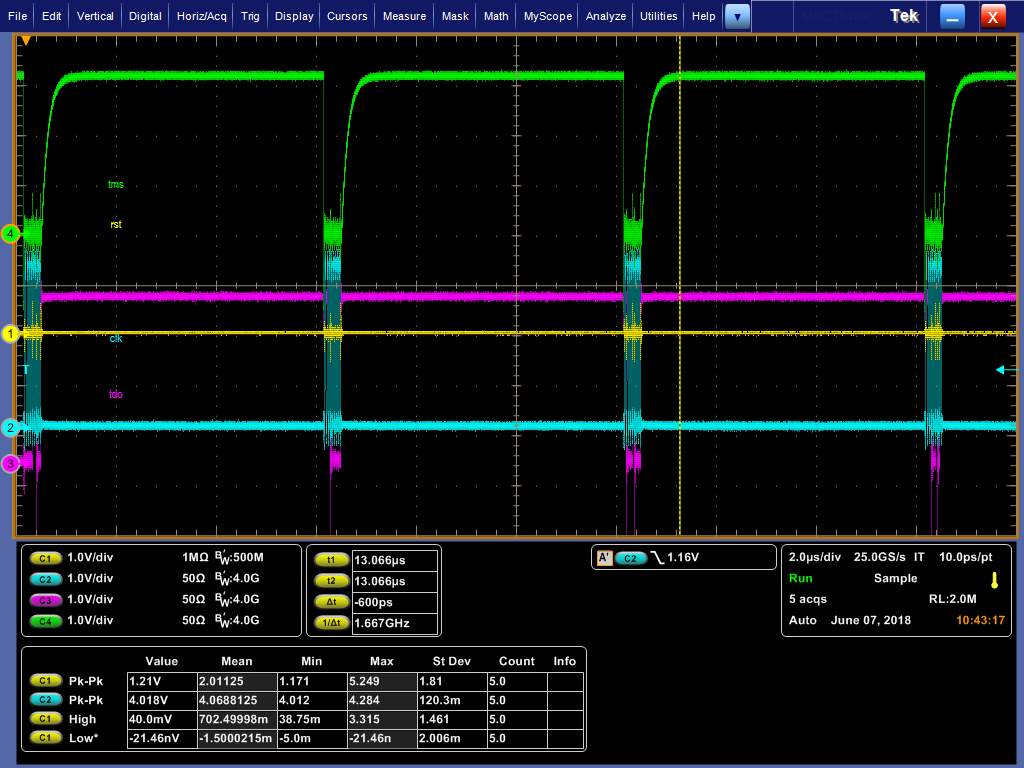

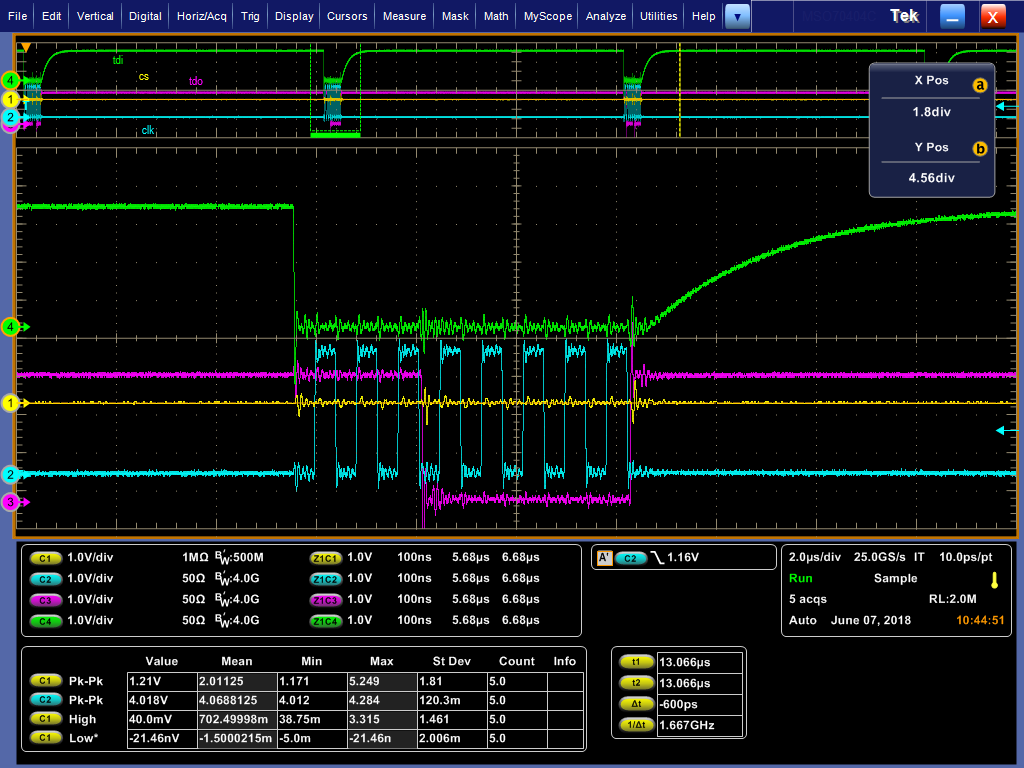

I have had a look now, why it takes so long. I see, that the flash is read by something around 25Mhz. But it read just one byte in 6µs. So it reads 8bits with 25MHz, and makes than a break for 6µs, before it reads the next eight bits.

It doesn't makes much sense to me, that the amic waits 6µs, before it reads the next byte, because it just needs to write this stuff to its memory, so it shouldn't be a big deal, right?

Is there anything I can change in the bootloader, to make it read the image faster?

The same question is valid for writing the flash from the PC. Is there a way to make this faster? For me it takes approximately 30 minutes to write the image.

Best Regards,

Stefan