Other Parts Discussed in Thread: OMAP-L138, OMAPL138

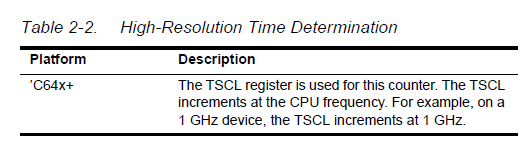

I am using the Logic PD Experimenter with OMAP-L138 SOM. I am trying to determine how to interpret the value returned by CLK_gethtime. My DSP is running at 300MHz. The crystal oscillator is running at 24MHz. So what is the clock rate of Timer 1?

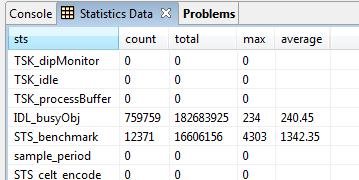

Here is the clock manager GUI:

The OMAP-L138 data sheet implies (vaguely) that the timer is driven by OSCIN (which I assume is 24MHz) cycle time x4. See below:

So this would lead me to believe the value returned by CLK_gethtime is;

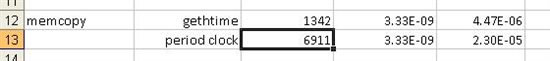

value_returned=(1/24MHz)*4 = 167ns?

Is this correct? From other measurements I have made it appears to be closer to 6.7ns.

Can someone give me some guidance on this?

thx

MikeH