Other Parts Discussed in Thread: CDCI6214, CDCM6208, CDC421A125

Can you suggest any wide temperature range (+105C or above) clock devices that can be used to provide the various clocks required for the AM5K2E0x Processor?

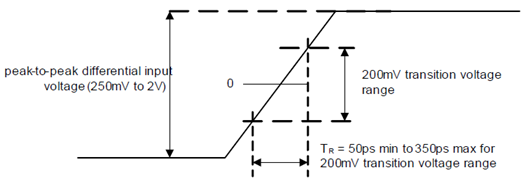

The processor datasheet indicates a minimum 250 mV (pk-pk) amplitude is required for the CORECLK, SGMII0CLK, DDR3 PLL DDRCLK and USB CLK together with rise and fall time requirements of

50ps to 350ps measured on 10% to 90% of the minimum V(pk-pk) or 200 mV.

The datasheet requirements for the NET CP PLL NETCPCLK are even more stringent since the datasheet suggests rise and fall time requirements 50ps to 350ps measured over 250 mV. (as opposed to 200mV shown in the hardware design guide SPRABV0—March 2014)