Dear Champs,

Is it possible to attach NOR and NAND flash memory can be attached on EMIF16 with same CS#?

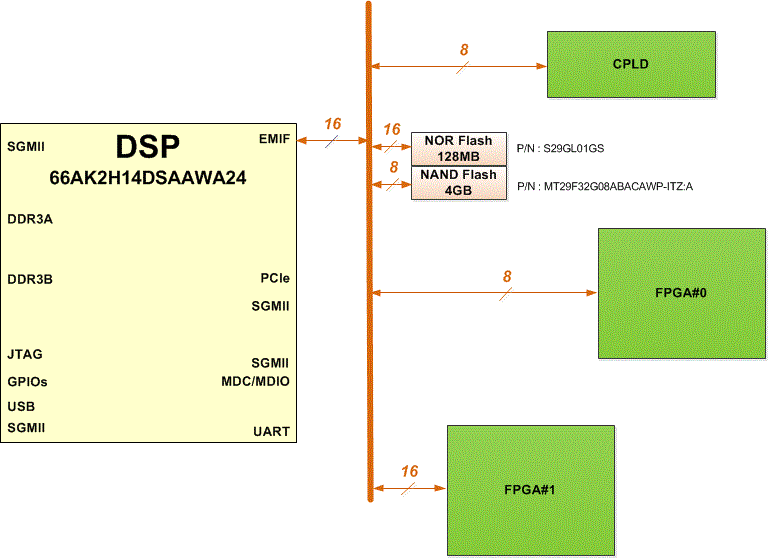

Actually my customer wants to attached 5 devices on EMIF16 as below and I would like to check if this is possible or not and if there is any performance degradation.

I think there should be no issue to FPGAs and CPLD with each CS#, but I'm very new to attach NOR and NAND flash memory on EMIF16 with same CS#.

e.g. FPGA0/1 and CPLD will use CS1 ~ 3, and NOR memory and NAND memory will use same CS0.

if possible, do you think there will be performance degradation in NAND flash memory and NOR flash memory, FPGAs?

The part name of flash memories are as below.

-. NOR Flash : SG29GL01GS ( Spansion )

-. NAND Flash : MT29F32G08ABACAWP-ITZ:A ( MICRON )

Thanks and Best Regards,

SI.