Customer reporting issue with EDMA3 UART

- Setup an EDMA3 circular buffer to receive UART input. The EDMA3 sets up to be auto reload.

- Setup an EDMA3 for EMIF16 input of 16K audio data. The data come in 1.33ms. When EDMA3 completes, its ISR submit another transfer, hence continuously going this way.

Observations:

- UART can receive small number of bytes without problem, anything around than 10 bytes.

- When UART receives more than 30 bytes, It shuts down. Meaning the UART will not receive any data. They can see UART line has received data on scope. But the its holding register shows previous value without change.

- If they stop EMIF16 EDMA3, UART can received 50K of continuous data without problem. UART running at 915000 baud, and its FIFO is enabled.

- In UART line status register, there is no error indication.

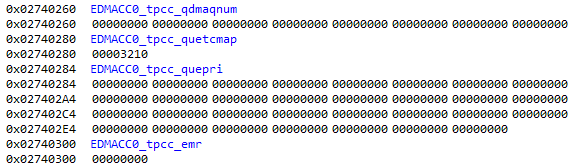

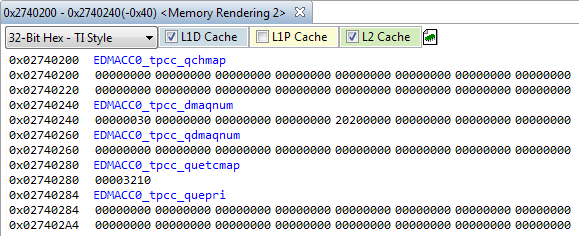

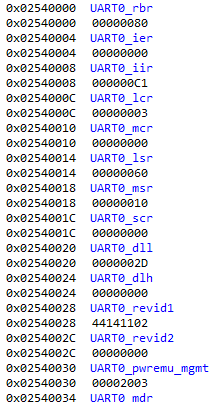

UART and EDMA3 setup: