Other Parts Discussed in Thread: TMDSICE3359, CCSTUDIO,

Hi Ti expert,

================Environmental description===========================================

- Custom Board with processor AM3352

- SDK-File:ti-processor-sdk-linux-am335x-evm-04.03.00.05

- Boot via SD-CARD, Using the create-sdcard.sh to build a 2 partition sd card (boot and rootfs)

- Base of our configuration is the AM335x-EVMSK configuration

=============================================================================

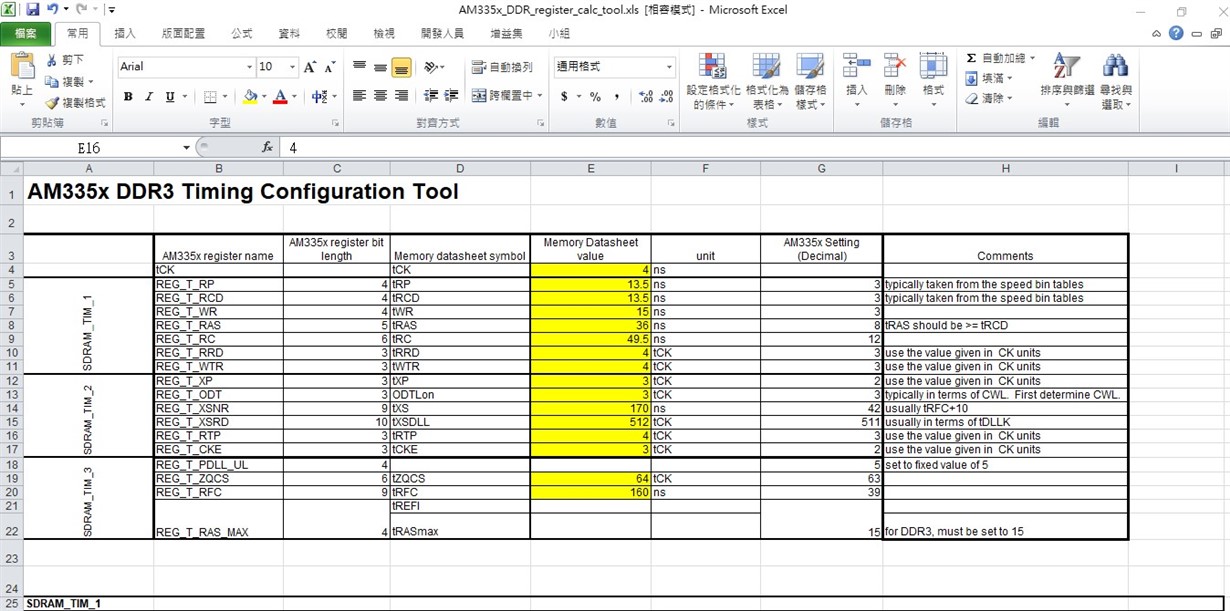

I currently use two examples to modify the internal DDR CLK of board.c

Ex1

If(board_is_evm_sk())

Config_ddr(400,&ioregs_evmsk,&ddr3_data,

&ddr3_cmd_ctrl_data,&ddr3_emif_reg_data,0);

Ex2.

force to set below setting instead of recognizing Board_ID

if (board_is_evm_sk())

config_ddr(400, &ioregs_evmsk, &ddr3_data,

&ddr3_cmd_ctrl_data, &ddr3_emif_reg_data, 0);

I hope to modify DDR clock changed from 303 to 400

But the amount of EE has not changed, the same is 300 CLK。

My way is to change the build code.

Then overwrite the MLO with u-boot.img to the boot partition of the SD card.

Is this correct?

Could you give some suggestions for me? Thank you.

BR

Egbert Liu