Part Number: DRA78

board : dra78x custom board

example for reference : pdk_dra7xx_1_0_10/packages/ti/csl/exampl/mcasp/mcasp_transmit

changes :

| example | my source | |

| trigger | edma event | polling |

| slot number(TXFMCTL register) | 2 | 16 |

| used tx pin | AXR 0, 1 | AXR 2 |

| clock(ACLKS, FSX) | internal | external |

| mode | I2S | TDM16 |

| McASPn | McASP1 | McASP3 |

- This board has run mcasp properly in sysbios environment. But it needs to work without sysbios

- I have confirmed that XRFST, XSMRST, XSRCLR, XHCLKRST in the GBLCTL register is activated

- If I activate only one slot or use burst mode, it works fine(TXTDM = 0 or 1)

- If I activate more than one slot, it will not work(TXTDM = 2, 3, 4 .... 16)

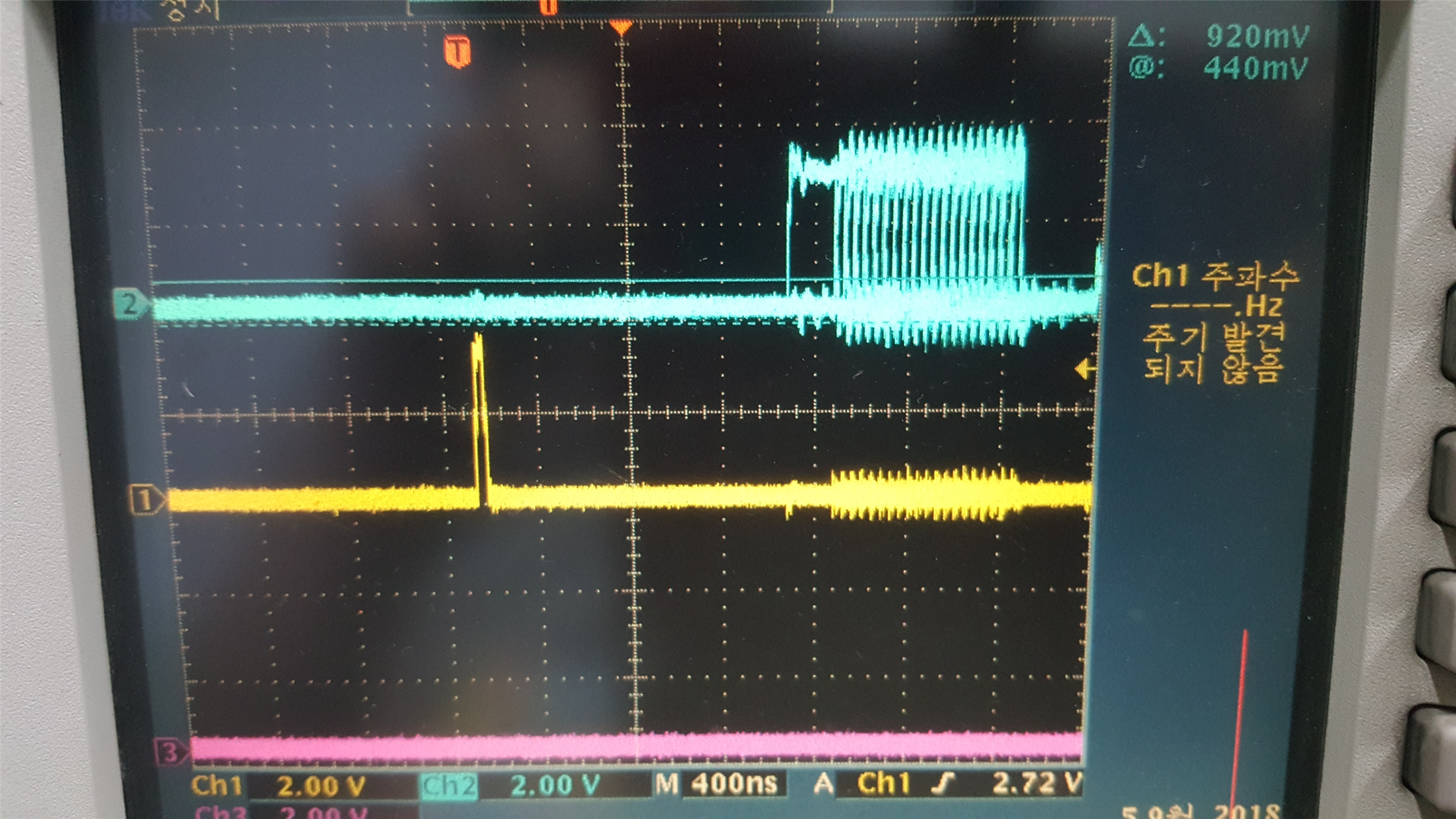

(1) Activate slot 0 only (oscilloscope ch1 : frame sync clk , oscilloscope ch2 : AXR 2, TXTDM = 1)

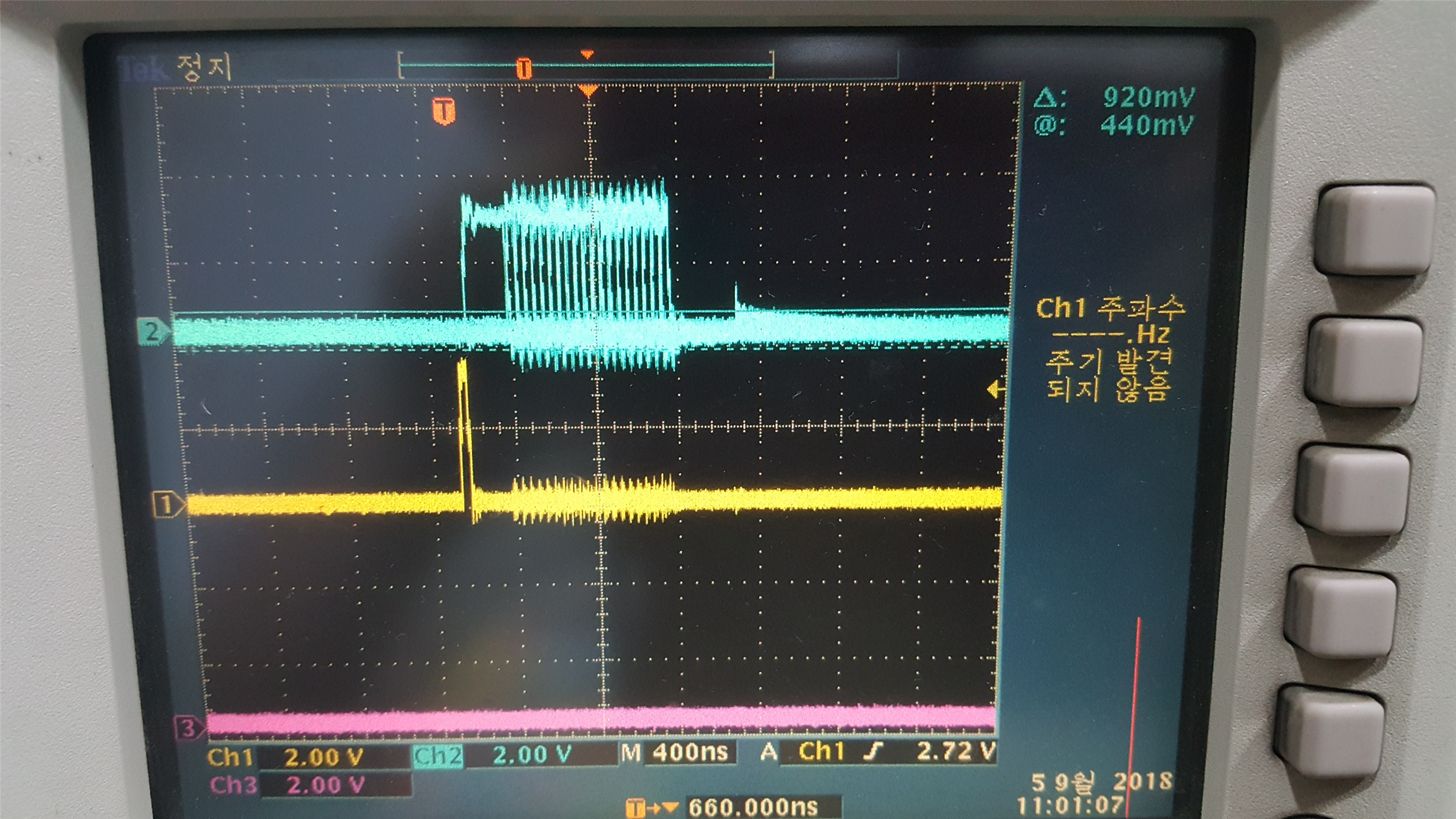

(2) Activate slot 1 only (oscilloscope ch1 : frame sync clk , oscilloscope ch2 : AXR 2, TXTDM = 2)

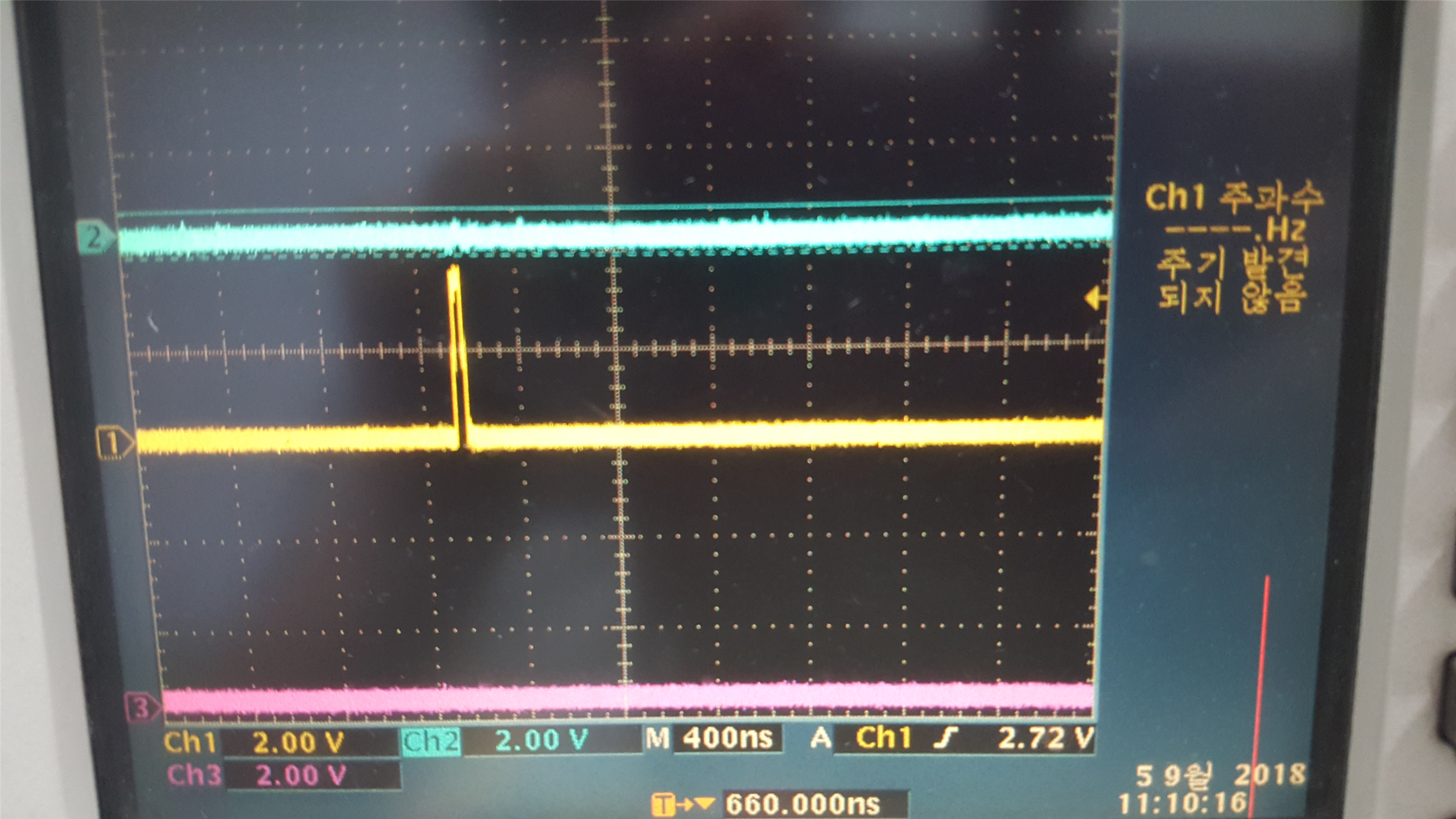

(3) Activate slot 0, 1 (oscilloscope ch1 : frame sync clk , oscilloscope ch2 : AXR 2, TXTDM = 3)

Thank for your help.