Dear Team,

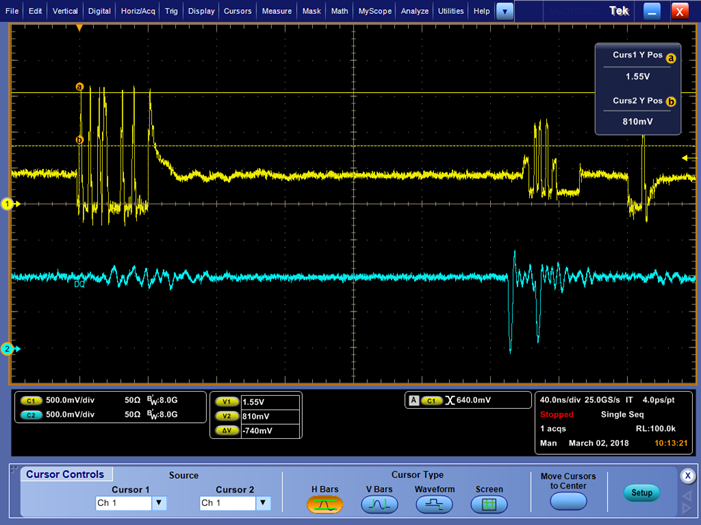

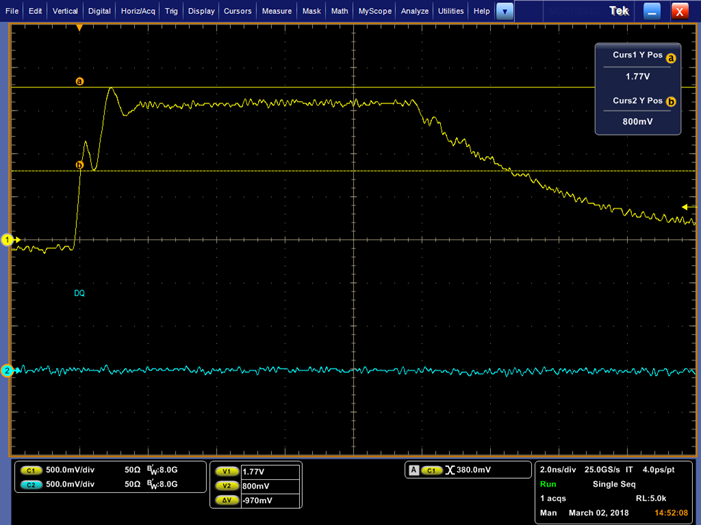

our customer has problems with the shapes of the signals on the data traces (using AM3358BZCZA100 and MT41K256M16TW memory).

The signals have been captured with an oscilloscope and analyzed. We have a written report and the design files that we would like to share offline.

With whom may we contact to analyze it?

Thank you,

Kind regards