Tool/software: TI-RTOS

Hi,

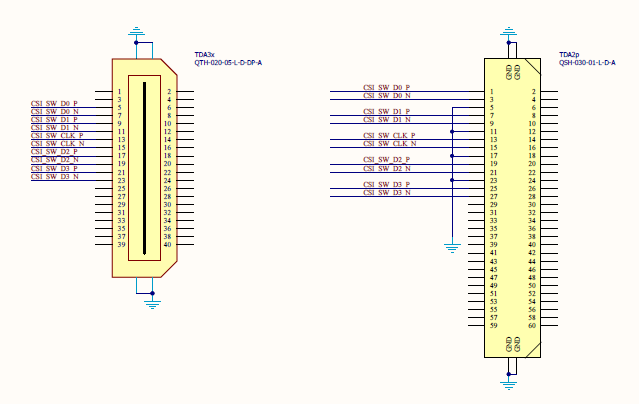

I have some adapter board which sends some video on CSI2 port and I want to connect that board with TDA3x-EVM to receive transmitted data.

The problem I have is that I can't get any data and RESET_DONE bit is not set in CAL_CSI2_COMPLEXIO_CFG register (0x4A054213). Assuming clock lane and data lanes are correctly mapped, polarity mapping is correct and frames are being sent (checked with oscilloscope) - what could be the problem. If I remember, there is some important thing about timings - video streaming must start at specific time? These are two different boards, so I have to start them independently.

Best Regards,

Stefan.