Hi All,

I would like to report a very strange behavior on VDINT0 interrupt on 6437.

According to the document description, VDINT0 follows every VD, for which there should be 60 VDINT0 interrupts (NTSC's BT.656 sampling) every second. But I record hundreds of thousands of them.

I have configured the interrupt control register to map VDINT0, whose event number is 24, to CPUINT4 by the follow code:

Interrupt controller configuration said:

extern far unsigned int ISTP_START;

extern cregister volatile unsigned int ISTP, IER, ISR, CSR;#define INTMUX1 *( volatile Uint32* )(0x01800104)

main()

{

ISTP = (unsigned int)(&ISTP_START);

IER |= (1<<4) + (1<<1); // set INT4 and NMIE

CSR |= 1;

INTMUX1 = 24; // maps...

}

And I have added a global counter within the ISR to count the number of VDINT0 interrupts:

interrupt service routine (ISR) said://global variables, initialized to 0

int count_int=0;

long long count_long_long=0;interrupt void my_isr()

{

count_int++;

count_long_long+=1;

}

This my_isr() is extremely short so there is no possibility for nesting, or interrupting with other code. Contrary to my expectation that both counters (use two like a double check) should increment with every new field which is 60 per second, they actually increase their value for over 100000 per second, almost unbelievable.

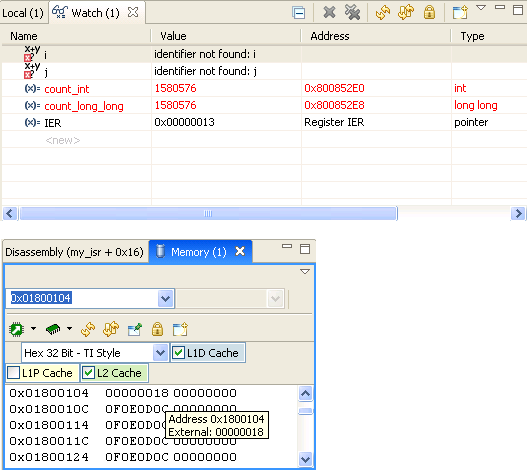

Here is the screenshot showing very large quantity after seconds of running:

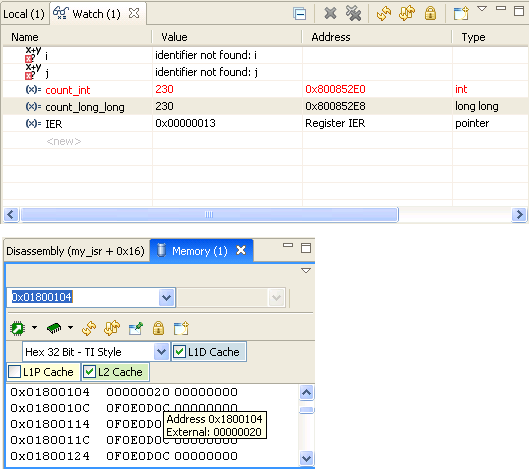

As a comparison, and also to ensure that the interrupt controller is configured and working properly, I map VPBE's VENCINT to CPUINT4, which also indicates end-of-frame event. In this way my_isr() is being triggered by VENCINT which happend 60 times per second. The experiment runs as expected and the following screenshot show the counter value after around about 4 seconds:

To summarize:

1. If CPUINT4 mapped to VPBE's VENCINT, everything is fine.

2. If CPUINT4 mapped to VPFE's VDINT0, the counter seems to show that there are hundreds of thousands of VDINT0 interrupts per second.

Does any one know the cause or could provide any suggestion?

Another question is that do I need to capture all these interrupts myself, rather than using DSP/BIOS? Could there be any pitfall in doing this?

Sincerely,

Zheng