Hi, All

I have two types of board with OMAPL137. One of the two types, is designed without "Power-on sequence."

At first both types were fully functional but, few monthes later, one without the "Power-on sequence" had a common problem.

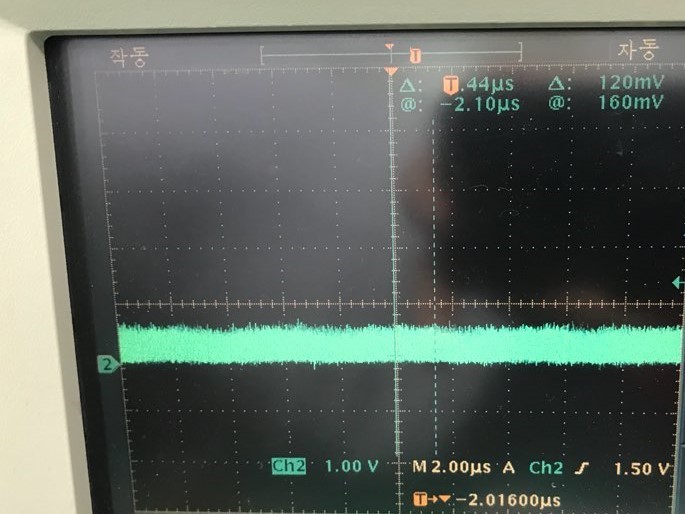

Communicating with SDRAM failed and I think EMIFB_CLK is the main cause, could there be other cause?

Does not keeping the boot sequence cause similar problems? Like LATCH-UP?

* EMIFB_Clock