Part Number: AM5708

Dear Sitara Team,

our customer sees an issue with the timing of the eMMC connected to the AM5708.

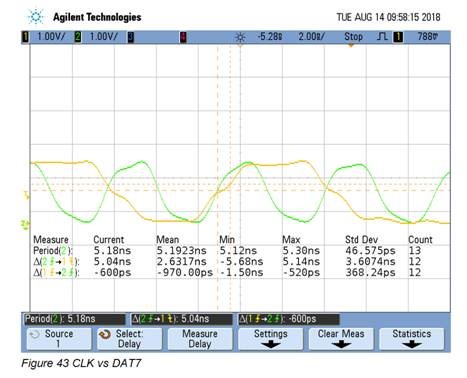

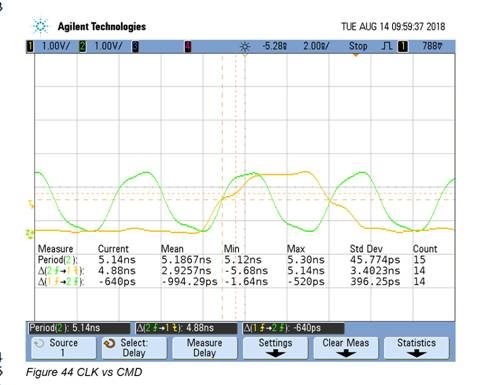

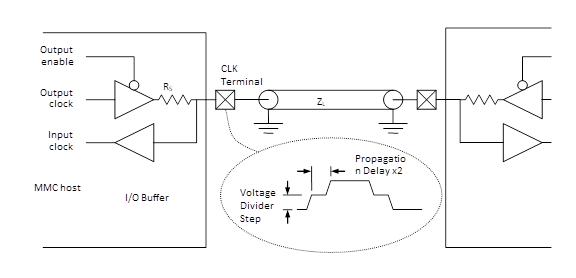

There are negative setup times for the CMD versus CLK and CLK versus DATA. The clock of eMMC is running of 200MHz, HS200 mode.

A few scope pictures are represented below:

During the project the clock frequency is increased from 50MHz to 200MHz. The timing with a clock frequency of 50MHz is OK.

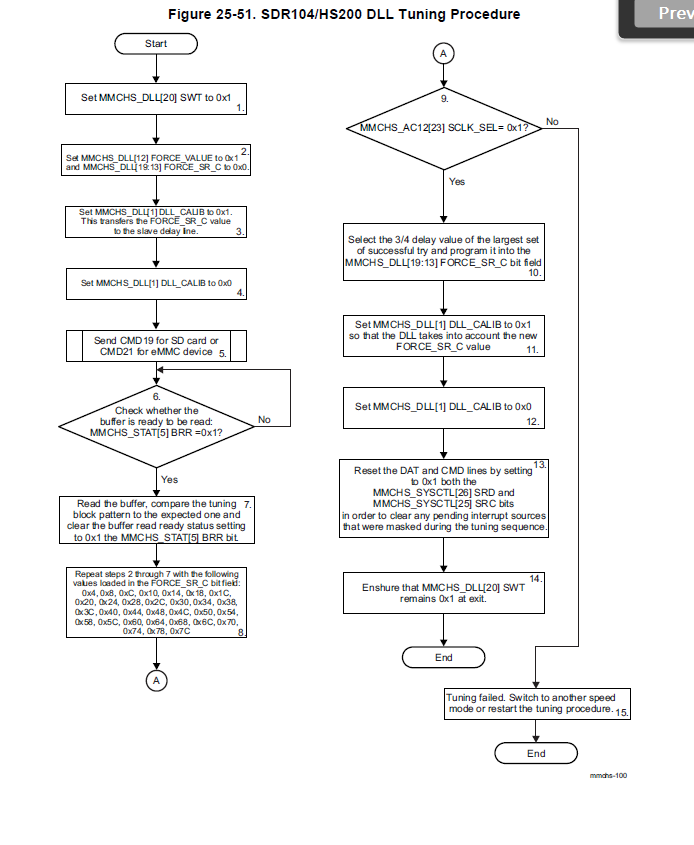

They noticed that the eMMC is never tuned in HS200 mode as described the SPRACA9.

They found the following in the TRM about it:

Questions:

- Does this tuning procedure also take care of the timing between CMD and CLK?

- Do we have to perform the tuning each time when the system is started? Or can it be a fixed register setting in Uboot?

- Do we have to perform the tuning in Uboot or in the Kernel?

- Does TI have software available for the tuning process?

Thanks and best regards

Martin