Other Parts Discussed in Thread: OMAPL138, OMAP-L138

Hi,

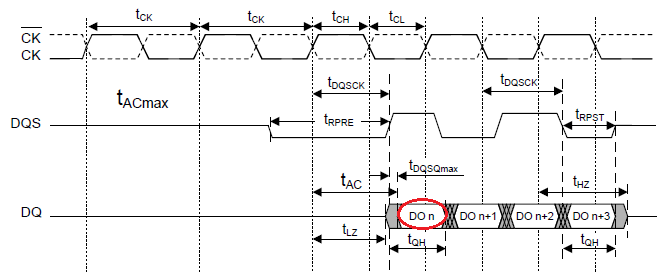

With reference to WinBond DRAM diagram below,

So if we were to interface this with OMAPL138,

1) Will the data "read" state based on DQS or CLK?

2) What will the "valid data window" to implement for the stage highlighted red above?

Regards,

Leo