Hi,

I have a question about the serial port interface of the TMS320VC33PEG150.

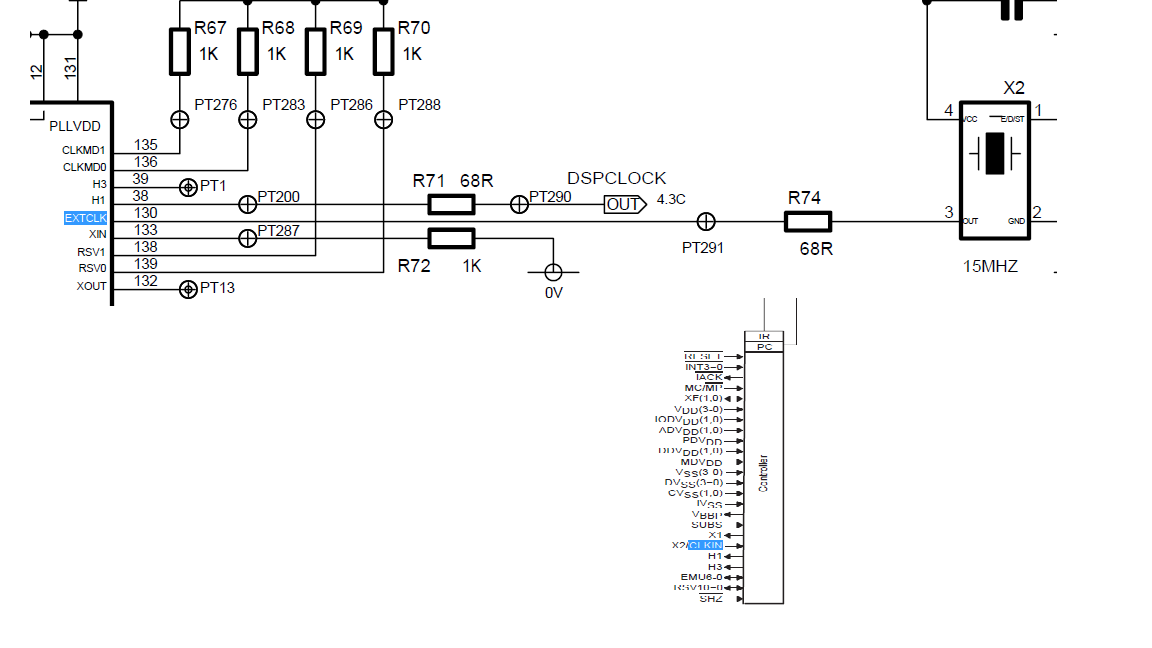

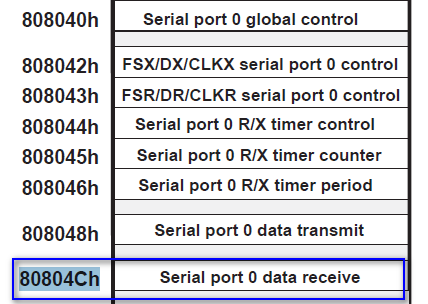

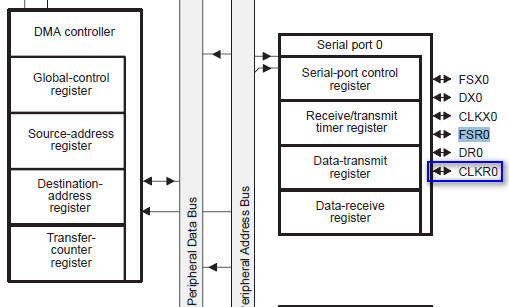

we have a very old product used this chip for many years. and it use this serial port to receive the Sample data. the serial port worked in the external clock mode. and the DSP input clock crystal of 15MHz and PLL output clock= 75Mhz. recently we want to increase the frequency of the serial port interface from 1.25Mhz to 5MHz, but find some error in the received data.

i see a description about the maximum frequency of the serial port in the page 12-42 of datasheet(SPRU031f.pdf): The maximum clock frequency for serial transfers is f(CLKIN)/4 if the internalclock is used and f(CLKIN)/5.2 if an external clock is used.

but i don'k find where the description of the CLKIN. it means the CLKIN is the pin130 (EXTCLK) ,so the maximum = 15Mhz/5.2=2.84Mhz ? or the output of the internal PLL, so the maximum = 75Mhz/5.2=14.42Mhz?

could you help to answer this question?

thanks your very much.

B.R.

yong