Hello,

As we know there are two options for system clock and oscillator input.

- External crystal+internal oscillator system

- External Clock (+ disabling internal oscillator

There are two matters attracted my attention and I like to discuss them here.

The first subject:

I always use one of these two options in my designs, either an external oscillator like 12 MHz NX3225SA or an oscillator module like a 12 MHz ASDMB as the external clock. Yesterday I was thinking of using both of them at the same time.

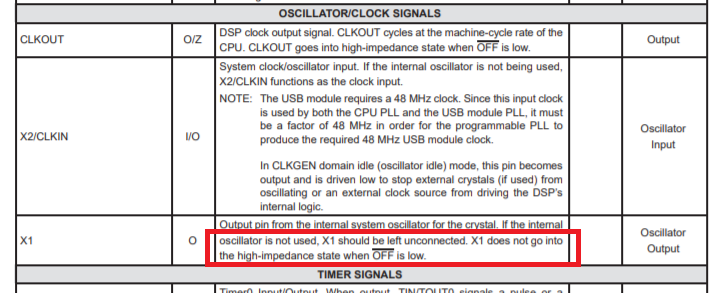

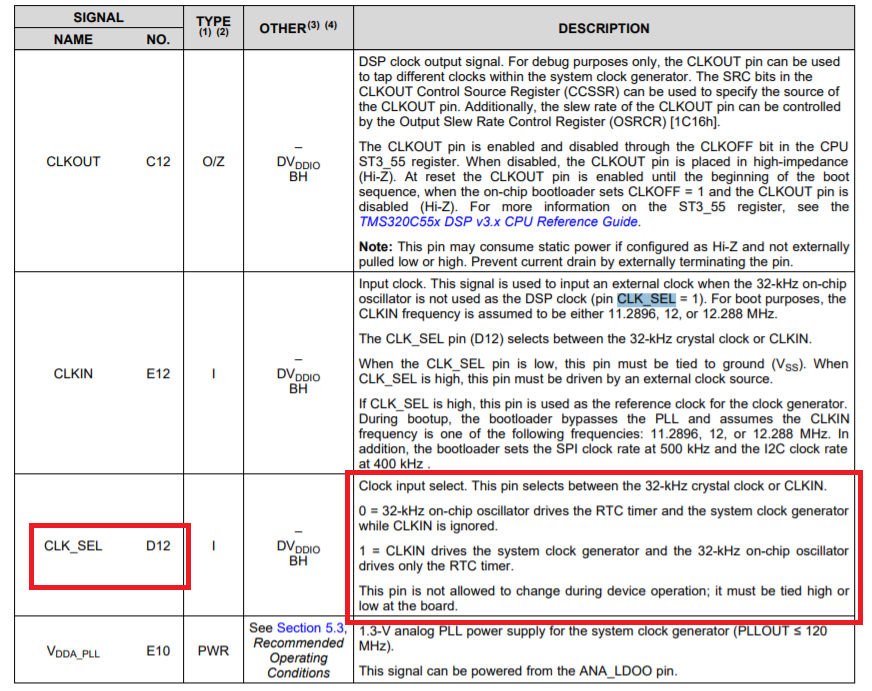

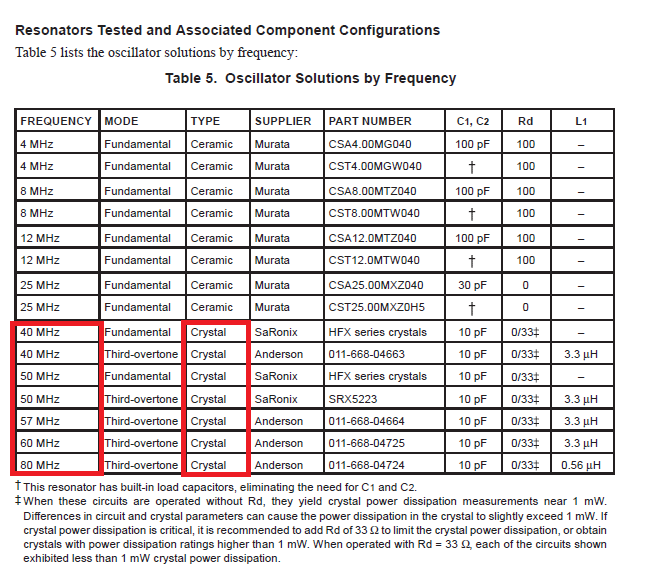

The image above has been taken from the datasheet of TMS3205509A and the image below has been taken from TMS320C5545.

Let's return to the main subject. Imagine that I'm using a TMS320C5545 and I want to use both of external crystal and oscillator module (clock) at the same time. Due to CLK_SEL and by using a simple jumper which can connect this pin to 1.8 v VCC or GND, simply we can switch from external crystal to oscillator module (clock) and vice versa. But what if I want to use e.g. a tMS320VC5509A. This processor is not completely similar with TMS320C5545 and there is not any pin like CLK_SEL which let us switch between two options of clock input?

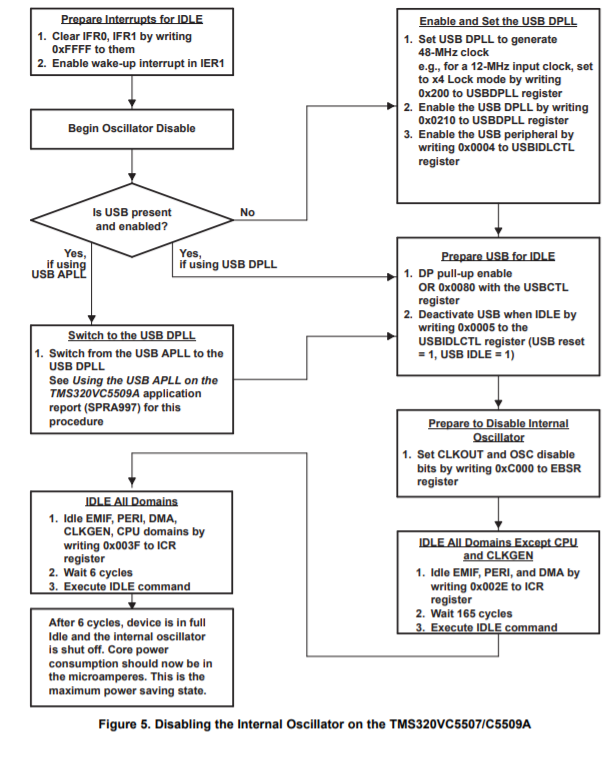

For example, when we are using an external crystal both X1 and X2/CLK are connected to the crystal's pins and simultaneously the output terminal of the clock oscillator is connected to X2/CLK. Again I have the idea for disabling the internal oscillator of DSP when I want to switch from crystal option to oscillator clock. The image below.

But the question in my mind is about the red box in the first image describing the status of X1 when the internal oscillator is disabled. It says the X1 terminal in this mode should be unconnected, while as I mentioned before I'd like to use crystal and oscillator at the same time so X1 is could not be unconnected. Therefore what would happen?

But the second matter:

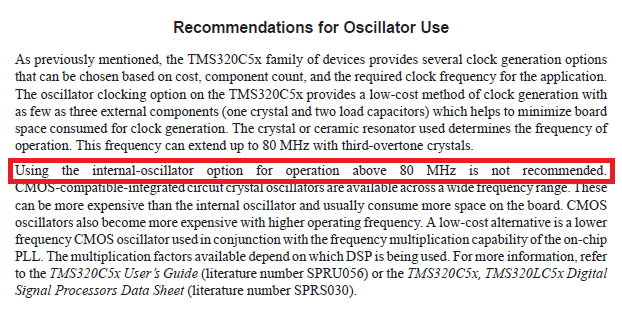

I was reading a document under the name SPRA054 (Use of the TMS320C5x Internal Oscillator With External Crystals or Ceramic Resonators Application Report) that a strange statement got my attention. Take the image below and the red box.

Ok, it's clear enough to understand the limitation of the internal oscillator for operation above 80 MHz. The matter is to carry out an operation in the maximum frequency of CPU (e.g. for TMS320VC5509A is 200 MHz)

The first condition is to ser CVDD to 1.6 v.

The second condition is to generate the clock with this frequency. There are three methods to do this:

-

External clock input with capability to divide the clock frequency by two

- External clock input to an on-board phase-locked loop (PLL) which can multiply the clock

frequency by one, two, three, four, five, or nine - Internal clock generation from an on-board oscillator with no external clock necessary

From the red box in the last image we can conclude that the method number 3 is not sufficient to reach 200 MHz of operating frequency. There are two other remaining ways, one is to use a 400 MHz oscillator clock and the second way is to use 40 MHz oscillators and with the help of on-board PLL we can reach 200 MHz by multiplying the input clock by five. The second method is my usual technique whenever I need to have an operation at the maximum frequency (200 MHz).

Is there anyother suggestion?

Regards,

Hossein