Tool/software: TI-RTOS

Hi

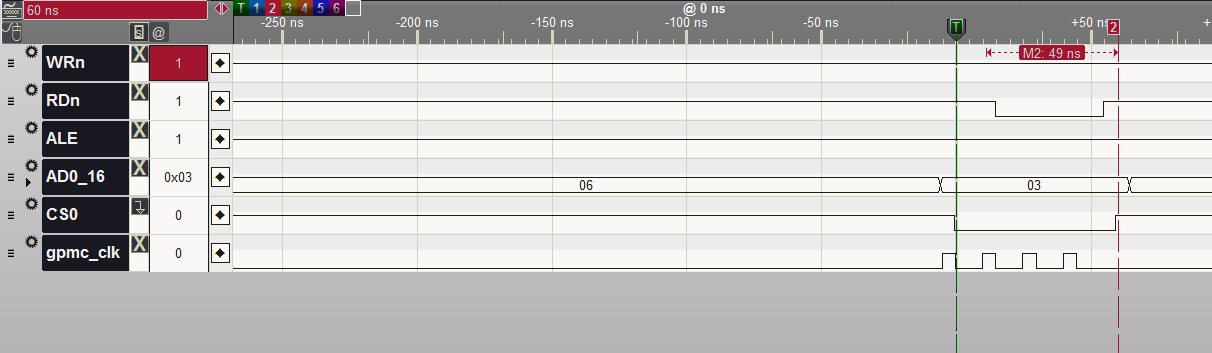

I'm braking my head on GPMC configuration in 16-bit address/data multiplexed mode.

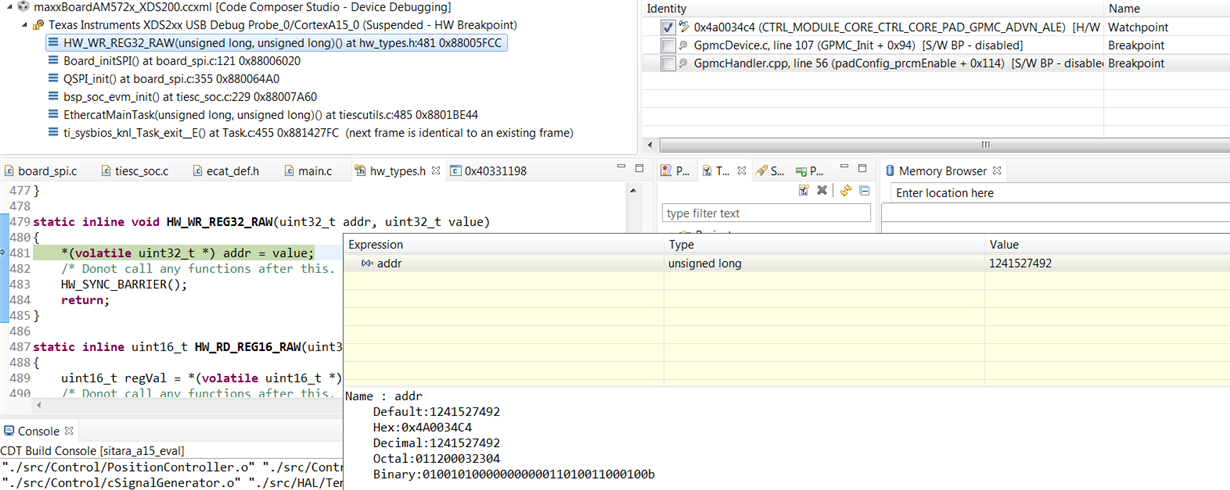

GPMC_ADVN_ALE is not coming out of CPU !!!

1. I set bits 9:8 MUXADDDATA to 0x2 as suggested.

2. Traced down to assembly that I write 0x28001200 to 0x50000060

3. Pin configuration

HW_WR_REG32(CSL_MPU_CORE_PAD_IO_REGISTERS_REGS+CSL_CONTROL_CORE_PAD_IO_PAD_GPMC_ADVN_ALE,0x10000);

4. CS control registers 0..6

0x28001200,

0x80881,

0x60594,

0x10857096,

0x10F1111,

0x8F0000,

0x00000f48,

What else do I miss?

Thanks

Rasty

: