Hello everybody,

If we want to use USB module of a 5507/09A, since both of CPU_PLL and USB_PLL have a common clock input source and due to the 48 MHz frequency that USB module needs so the input clock should be a factor of 48 MHz sth like 12, 16, 24 and so on. Here there are two matters:

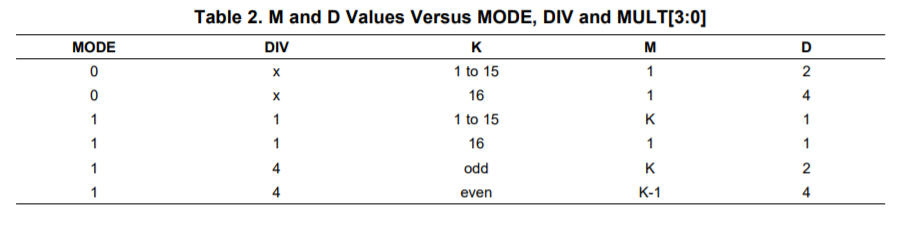

- Related to the mathematical relation between the frequency of the input clock of USB_PLL and frequency of the generated clock of this unit, F(input_clk)*(M/D)=F(APLLUSB_clk) and the accepted values for M and D based on the image below which is taken from spra997b, we can conclude that input clock frequency could be more or less than 48 MHz.

- On the other hand, assume that the maximum CPU frequency is 200 MHZ and the power condition for achieving this frequency is supplied. OK, now consider I want to use the USB module and to use the device at the maximum CPU frequency, 200 MHz. What are the suggestions for input clock and M and D selection? Consider this fact that CPU_PLL unit can multiply the input clock (which is common with the input clock of USB_PLL as mentioned above) by 1,2,3,4,5,9 . Let me summarize the issue into two following simple equations:

- F(input_clk)*(M/D)=F(APLLUSB_clk)=48MHz (which M and D come from table below)

- F(input_clk)*CPU_PLL_coeffiient=200MHz (which CPU_PLL_coeffiient could be one these numbers 1,2,3,4,5,9)

Waiting for an idea.

Regards,

Hossein