Tool/software: TI-RTOS

Hi All ,

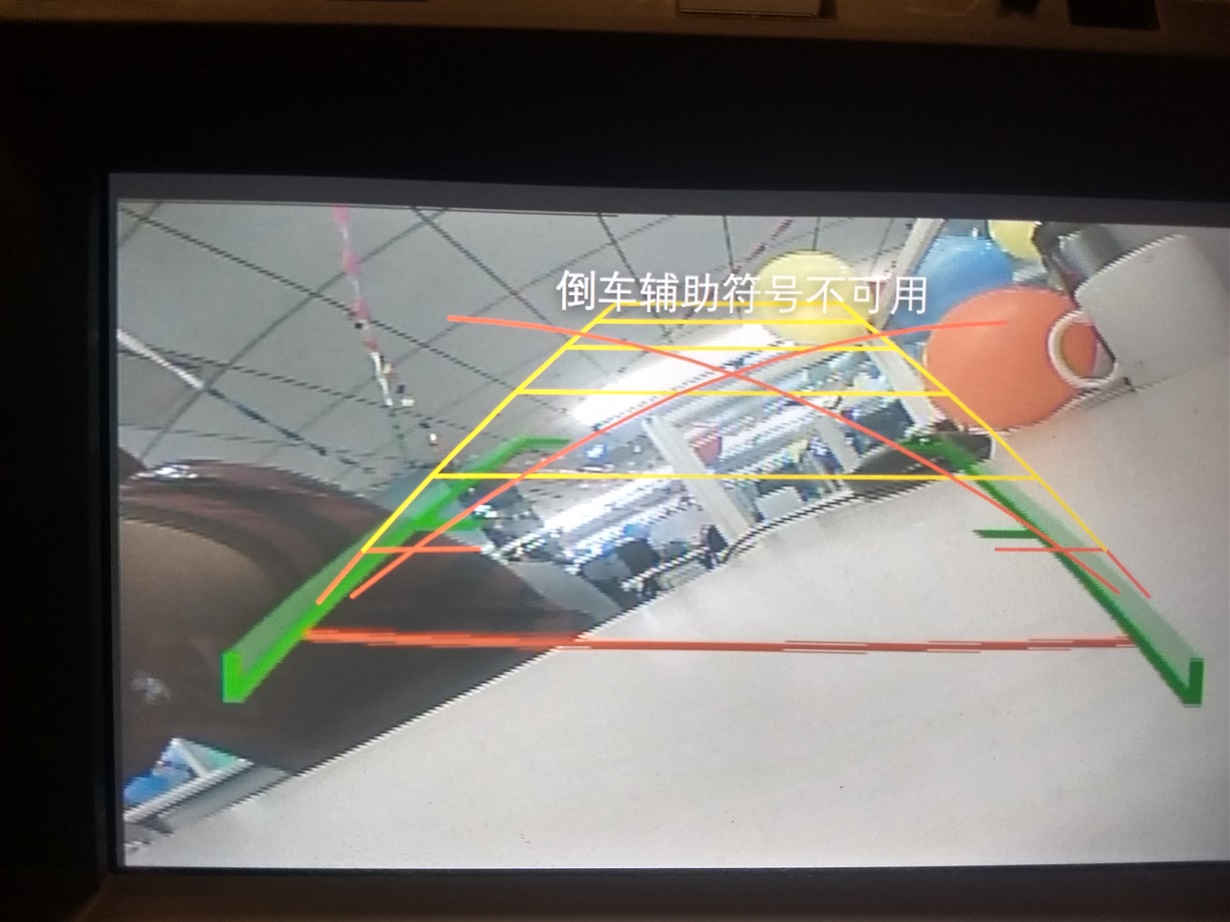

I am capturing BT-656 streams from decoder ADV7182 through Slice1 PortA of VIP parser through VPDMA. The frames are captured properly,but the every alternate lines in the frame looks missing.This results in pixels missing in the every alternate lines(Black lines on the roof) ,which results in not a smooth picture. What is the real cause for this issue.

We are using Vision SDK based driver in sysbios in ( IPU1-cortex-m4) for DRA74xx .

Have attached the original and zoomed version of the same snap shot. If close look the the zoomed.png file ,where the straight lines(black lines & on other edges) in the picture are discontinuous. Can some one let me know how this problem can be resolved.

With regards,