Now, I just want to complete a very simple data transfer from 'xmt ' to 'rcv' with EDMA3. I don't use the DSP BIOS, just use the CSLr. I use DMA chanell , not QDMA chanell.

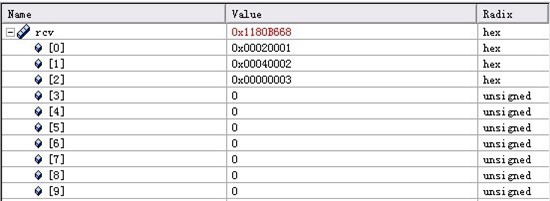

Question: After running the code, the data don't transfer from 'xmt' to 'rcv'.

Q1. After Step 5, I don't see any change in register ESR. Is this right? Has EVENT1 been triggered?

and the edma3ccRegs->EMR is 0. It is said that no event is missed .

Q2. Is there any error among the settings?

And I set the Register as follow:

1.Writing into EESR, enable the EVENT 1;

2.Set up DMAQNUM to map the EVENT 1 to the Queue 0;

3.Parameter set setup. chanell 1-->PARAMSET[1];

a)Channel Options Parameters----OPT----Transfer complete interrupt is disabled. And A-synchronized;

b)Channel Source Address Parameter---SRC----&xmt;

c)A Count/B Count Parameter---A_B_CNT----ACNT=N=10; BCNT=1;

d)Channel Destination Address---DST----&rcv;

e)Source B Index/Destination B Index Parameter--- SRC_DST_BIDX---DSTBIDX=0;SRCBIDX=0;

f)Link Address/B Count Reload Parameter---LINK_BCNTRLD--- BCNTRLD=1; LINK=Parameters Set 1 Byte address;

g)SRC_DST_CIDX---DSTCIDX=0;SRCCIDX=0;

h)CCNT=1;

4.Disable the interrupt in IER by writing 0 to IESR.

5.Manually-triggered EVENT1 by writing 0x0002 to ESR.

6.Wait for completion.

The code as follows,

edma3ccRegs->EESR |= (Uint32) 0x0002;

edma3ccRegs->DMAQNUM[0] = (CSL_EDMA3CC_DMAQNUM_E1_Q0 << CSL_EDMA3CC_DMAQNUM_E1_SHIFT);

edma3ccRegs->PARAMSET[1].OPT = (CSL_EDMA3CC_OPT_TCINTEN_DISABLE << CSL_EDMA3CC_OPT_TCINTEN_SHIFT)|\

(CSL_EDMA3CC_OPT_SYNCDIM_ASYNC << CSL_EDMA3CC_OPT_SYNCDIM_SHIFT);

edma3ccRegs->PARAMSET[1].SRC = (Uint32) &xmt;

edma3ccRegs->PARAMSET[1].A_B_CNT = (Uint32) 0x0001000A;

edma3ccRegs->PARAMSET[1].DST = (Uint32) &rcv;

edma3ccRegs->PARAMSET[1].SRC_DST_BIDX = (0x0000 << CSL_EDMA3CC_SRC_DST_BIDX_DSTBIDX_SHIFT)|\

(0x0000 << CSL_EDMA3CC_SRC_DST_BIDX_SRCBIDX_SHIFT);

edma3ccRegs->PARAMSET[1].LINK_BCNTRLD = 0x00014020;

edma3ccRegs->PARAMSET[1].SRC_DST_CIDX = (Uint32)0x00;

edma3ccRegs->PARAMSET[1].CCNT = (Uint32)0x01;

edma3ccRegs->IESR =0x00;

edma3ccRegs->ESR |= (Uint32) 0x0002;

while(!(edma3ccRegs->IPR & 0x0002));