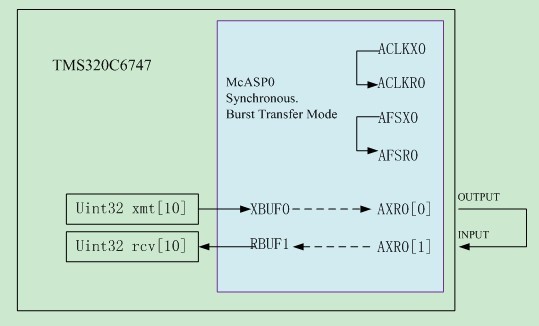

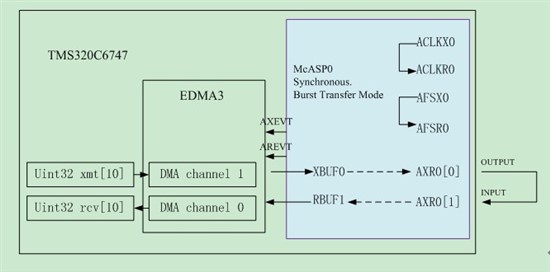

I'm successful in sending and receiving data with MCASP0 no EDMA3. Then I want use EDMA3 to serivice for MCASP data transfer.

MCASP is working in Burst Transfer Mode, and data is transfered from AXR0[0] to AXR0[1]. I want to transfer 10*Uint32 from the 'xmt' to 'rcv' with MCASP0 that is serviced by EDMA3. There is No interrupt in MCASP and EDMA3.

In MCASP0, the code settings that support EDMA3 as follows,

mcasp0Regs->RFMT = (Uint32) 0x000000F0;

mcasp0Regs->REVTCTL = CSL_MCASP_REVTCTL_RDATDMA_ENABLE;

mcasp0Regs->XFMT = (Uint32) 0x000000F0;

mcasp0Regs->XEVTCTL = CSL_MCASP_XEVTCTL_XDATDMA_ENABLE;

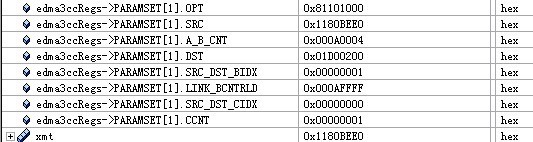

And EDMA3 settings are:

1.EDMA3 data sending

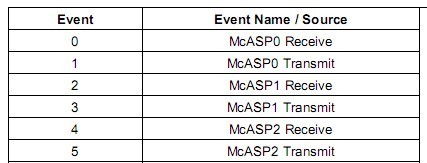

edma3ccRegs->EESR |= (Uint32) 0x0002;

edma3ccRegs->DMAQNUM[0] = (CSL_EDMA3CC_DMAQNUM_E1_Q0 << CSL_EDMA3CC_DMAQNUM_E1_SHIFT);

edma3ccRegs->PARAMSET[1].OPT = (CSL_EDMA3CC_OPT_TCINTEN_ENABLE << CSL_EDMA3CC_OPT_TCINTEN_SHIFT)|\

(0x01 << CSL_EDMA3CC_OPT_TCC_SHIFT)|\

(CSL_EDMA3CC_OPT_SYNCDIM_ABSYNC << CSL_EDMA3CC_OPT_SYNCDIM_SHIFT);

edma3ccRegs->PARAMSET[1].SRC = (Uint32) &xmt;

edma3ccRegs->PARAMSET[1].A_B_CNT = (Uint32) 0x000A0004;

edma3ccRegs->PARAMSET[1].DST = 0x01D00200;

edma3ccRegs->PARAMSET[1].SRC_DST_BIDX = (0x0000 << CSL_EDMA3CC_SRC_DST_BIDX_DSTBIDX_SHIFT)|\

(0x0001 << CSL_EDMA3CC_SRC_DST_BIDX_SRCBIDX_SHIFT);

edma3ccRegs->PARAMSET[1].LINK_BCNTRLD = 0x000A4020;

edma3ccRegs->PARAMSET[1].SRC_DST_CIDX = (Uint32)0x00;

edma3ccRegs->PARAMSET[1].CCNT = (Uint32)0x01;

edma3ccRegs->IESR =0x00;

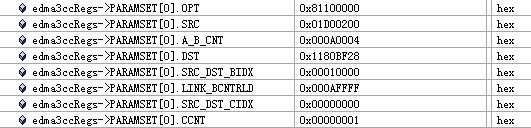

2.EDMA3 data receiving

edma3ccRegs->EESR |= (Uint32) 0x0001;

edma3ccRegs->DMAQNUM[0] = (CSL_EDMA3CC_DMAQNUM_E0_Q0 << CSL_EDMA3CC_DMAQNUM_E0_SHIFT);

edma3ccRegs->PARAMSET[0].OPT = (CSL_EDMA3CC_OPT_TCINTEN_ENABLE << CSL_EDMA3CC_OPT_TCINTEN_SHIFT)|\

(0x00 << CSL_EDMA3CC_OPT_TCC_SHIFT)|\

(CSL_EDMA3CC_OPT_SYNCDIM_ABSYNC << CSL_EDMA3CC_OPT_SYNCDIM_SHIFT);

edma3ccRegs->PARAMSET[0].SRC = 0x01D00200;

edma3ccRegs->PARAMSET[0].A_B_CNT = (Uint32) 0x000A0004;

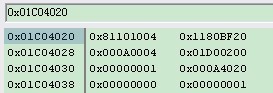

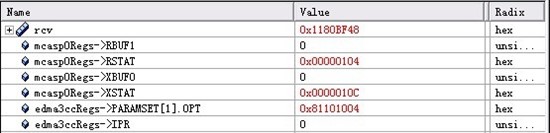

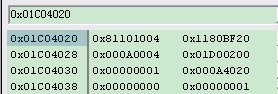

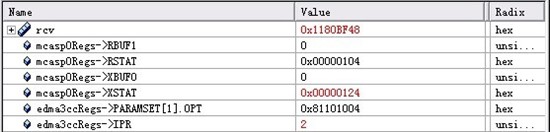

edma3ccRegs->PARAMSET[0].DST = (Uint32) &rcv;

edma3ccRegs->PARAMSET[0].SRC_DST_BIDX = (0x0001 << CSL_EDMA3CC_SRC_DST_BIDX_DSTBIDX_SHIFT)|\

(0x0000 << CSL_EDMA3CC_SRC_DST_BIDX_SRCBIDX_SHIFT);

edma3ccRegs->PARAMSET[0].LINK_BCNTRLD = 0x000A4000;

edma3ccRegs->PARAMSET[0].SRC_DST_CIDX = (Uint32)0x00;

edma3ccRegs->PARAMSET[0].CCNT = (Uint32)0x01;

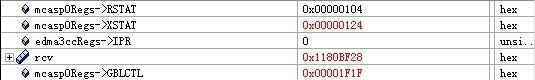

Then in main code, CPU is polling for the complete of sending and receiving.

while (!(edma3ccRegs->IPR & 0x0002));

while (!(edma3ccRegs->IPR & 0x0001));

After running the code, I saw:

IPR =2; XSTAT=0x00000124; RSTAT=0x00000104;

and the data in rcv is all 0. That means no data is received.

Is there any error in my settings?