Tool/software: Linux

Hello TI,

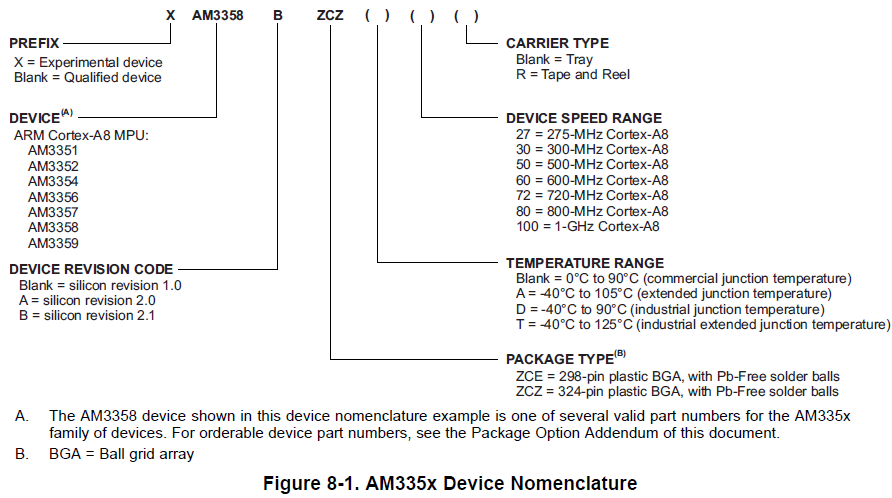

I am using custom AM3352 board with Micron NAND MT29F4G08ABBFA. Here i need to optimize the NAND Performance. As per the

Tweak NAND device signal timings using AM335x TRM

is not easy, Because TRM explains about NOR device signal timings (section 7.1.4.1) And There is no NAND device signal timings. Please guide me how to Tweak NAND device signal timings using Micron NAND MT29F4G08ABBFA data sheet.

(slow while reading from and writing to) below default gpmc setting i am using (from AM335x-evm.dts)

gpmc,device-width = <1>;

gpmc,sync-clk-ps = <0>;

gpmc,cs-on-ns = <0>;

gpmc,cs-rd-off-ns = <44>;

gpmc,cs-wr-off-ns = <44>;

gpmc,adv-on-ns = <6>;

gpmc,adv-rd-off-ns = <34>;

gpmc,adv-wr-off-ns = <44>;

gpmc,we-on-ns = <0>;

gpmc,we-off-ns = <40>;

gpmc,oe-on-ns = <0>;

gpmc,oe-off-ns = <54>;

gpmc,access-ns = <64>;

gpmc,rd-cycle-ns = <82>;

gpmc,wr-cycle-ns = <82>;

gpmc,wait-on-read = "true";

gpmc,wait-on-write = "true";

gpmc,bus-turnaround-ns = <0>;

gpmc,cycle2cycle-delay-ns = <0>;

gpmc,clk-activation-ns = <0>;

gpmc,wait-monitoring-ns = <0>;

gpmc,wr-access-ns = <40>;

gpmc,wr-data-mux-bus-ns = <0>;