Part Number: DM3730

Hello,

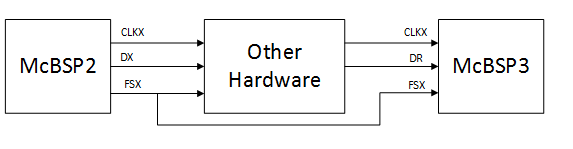

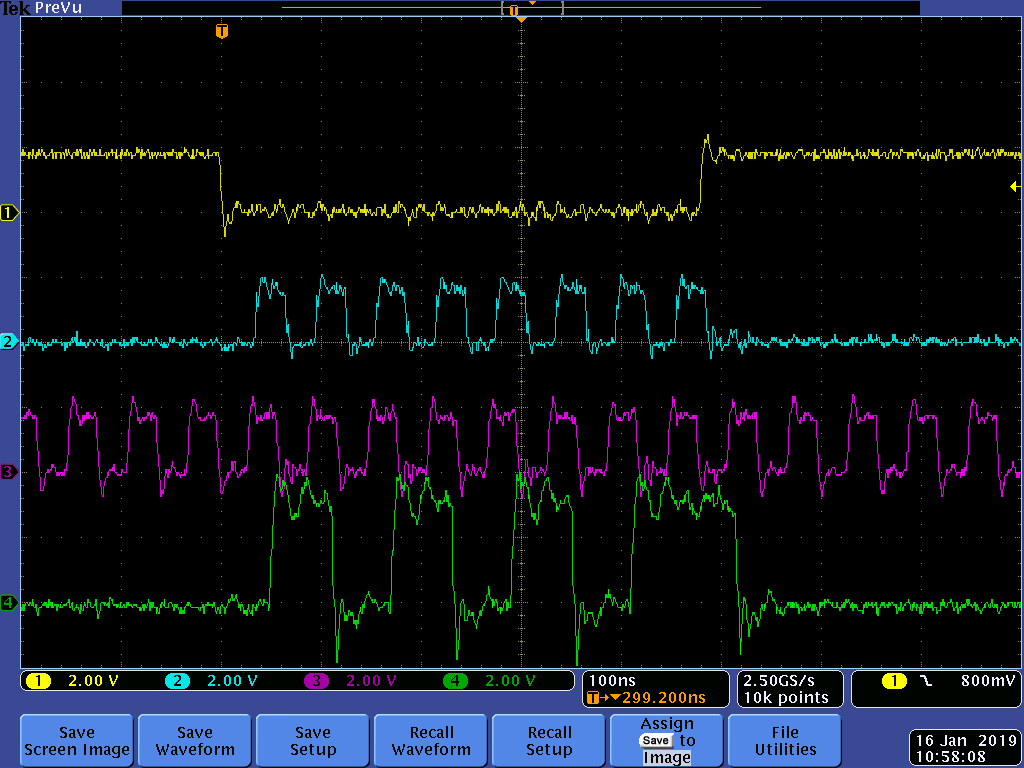

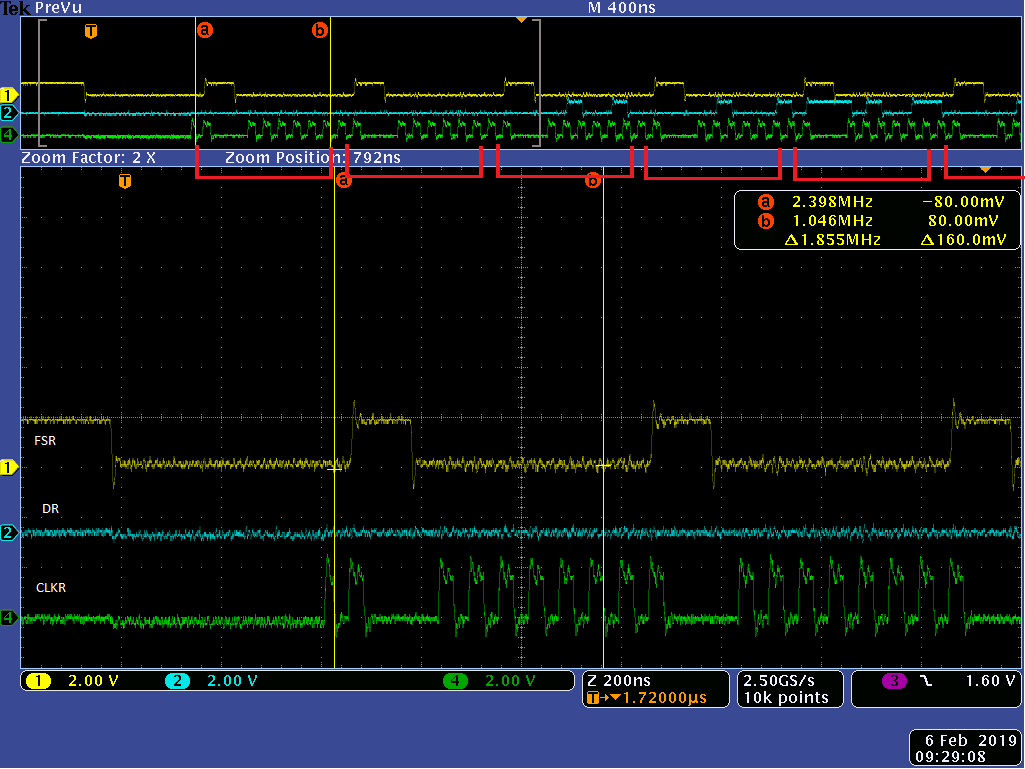

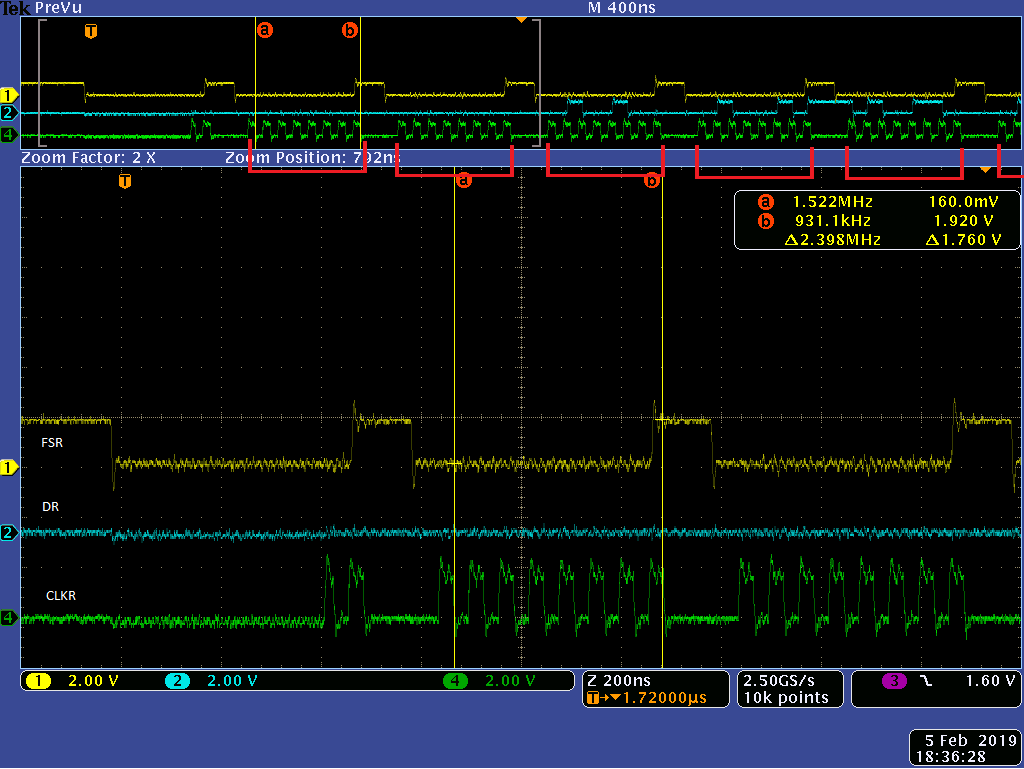

I am using McBSP2 and McBSP3 on a DM3730 processor to send data to and from another hardware device. My hardware configuration uses McBSP2 as a master to transmit data to the other device, and McBSP3 as a slave to receive data from the other device as per the attached diagram. Currently the hardware between the McBSPs is gating the clock to McBSP3 so that it is only present when FSX is active - as per the attached scope capture. Ch1 = FSX, Ch2 = CLKX input to McBSP3, and Ch3 = CLKX output from McBSP2. FSX is configured for active-low, 8-bit frames, 8-cycle pulse width. Data and Frame sync are sampled on the rising edge.

In this configuration we cannot receive data from McBSP3 - we can transmit any number of bytes from McBSP2, but the McBSP3 DRR register is empty afterwards. If we connect the free-running McBSP2 clock directly to McBSP3 and make no other HW or SW changes, we can receive data correctly. Can you help us understand why we are not receiving data?

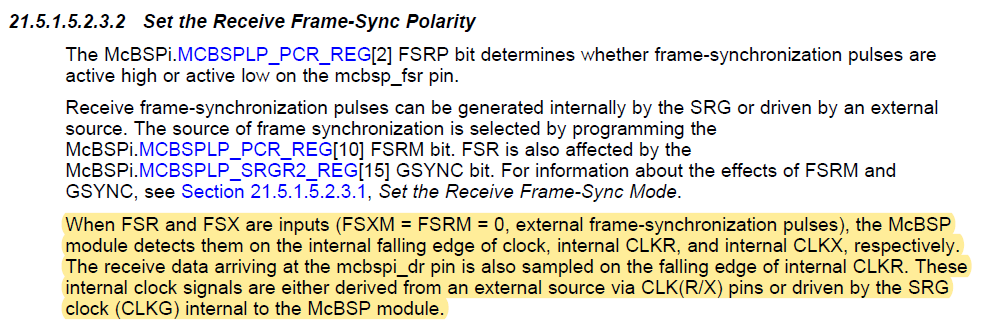

1. In our configuration McBSP3 never sees FSX inactive (high) on a rising clock edge. Does the McBSP need to sample frame sync inactive before sampling it active in order to recognize the start of a frame?

2. In our configuration McBSP3 CLKX stops after the end of the frame, and doesn't resume until the start of the next frame. Are any CLKX pulses required after the end of a frame to move the received data from the shift register to the DRR register?

Thank you for your help,

Steve