Other Parts Discussed in Thread: TEST2

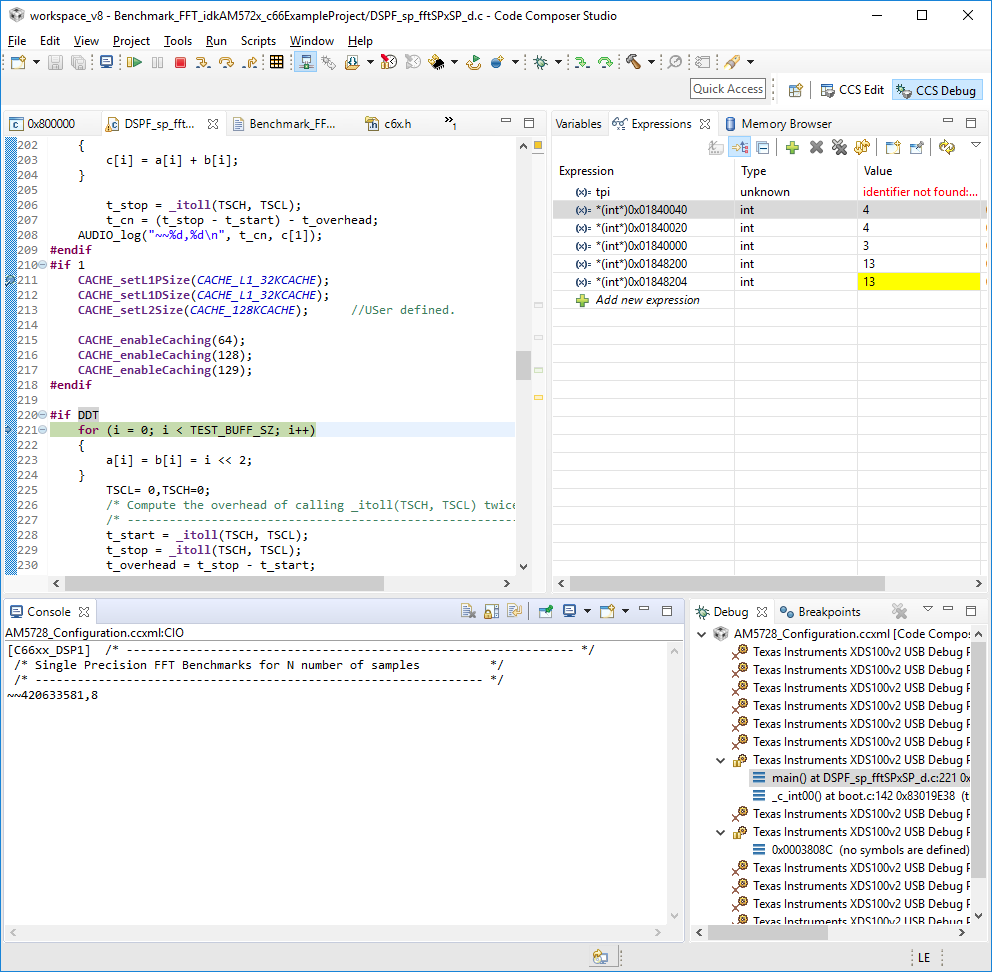

Tool/software: Code Composer Studio

Hi, kind TI and everyone,

I followed "TMS320C66x DSP Cache User Guide" 2.2, and tested VLIB_xyGradients() using AM5728 IDK and CCS8.2 as bellow:

main.c:

...

// for allocate into DDR

#pragma DATA_SECTION(ppin, ".ddr")

#pragma DATA_SECTION(ppgradx_opt, ".ddr")

#pragma DATA_SECTION(ppgrady_opt, ".ddr")

#pragma DATA_SECTION(ppgradx_cn, ".ddr")

#pragma DATA_SECTION(ppgrady_cn, ".ddr")

// for align with L2 cache

#pragma DATA_ALIGN(ppin, CACHE_L2_LINESIZE)

#pragma DATA_ALIGN(ppgradx_opt, CACHE_L2_LINESIZE)

#pragma DATA_ALIGN(ppgrady_opt, CACHE_L2_LINESIZE)

#pragma DATA_ALIGN(ppgradx_cn, CACHE_L2_LINESIZE)

#pragma DATA_ALIGN(ppgrady_cn, CACHE_L2_LINESIZE)

uint8_t ppin[HH * WW];

int16_t ppgradx_opt[HH * WW], ppgrady_opt[HH * WW];

int16_t ppgradx_cn[HH * WW], ppgrady_cn[HH * WW];

...

.cinit : load > L2_SRAM

.cio : load >> L2_SRAM

.text : load >> L2_SRAM

.stack : load > L2_SRAM

.const : load > L2_SRAM START(const_start) SIZE(const_size)

.far : load >> L2_SRAM

.switch : load >> L2_SRAM

.fardata : load >> L2_SRAM

.data : load >> L2_SRAM

.neardata : load >> L2_SRAM

.rodata : load >> L2_SRAM

.sysmem : load > L2_SRAM

.ddr : load >> EXT_MEM