Tool/software: TI-RTOS

Hi experts!

I changed "MCASP_Audio example" generated for evm572x (I've got beagleboard x15) to use interrupts instead of EDMA. I didn't use "mcasp_drv" but CSL mcasp library (sequences of programming took from TRM). All parameters of I2S-mcasp configuration used are the same as in example.

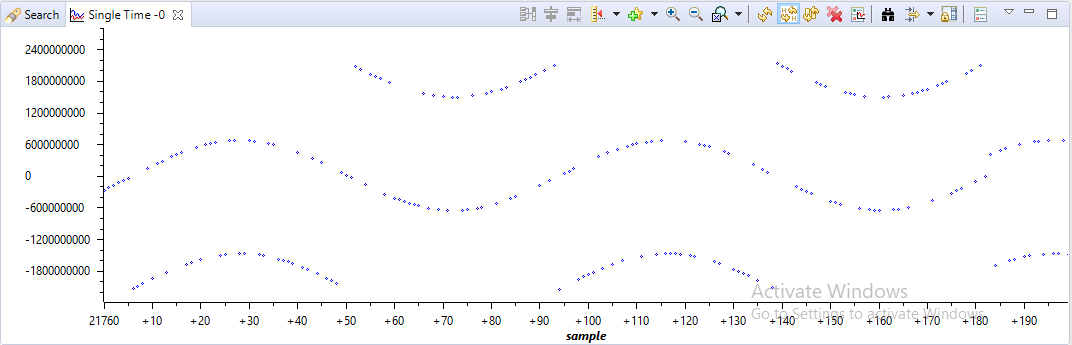

My problem is that MSB has random value - it can be see on the picture attached: (this is sinusoidal signal generated on the PC sound card and connected to board input)

(As U2 is used) I imagine that middle part of samples are with correct values. So samples that are placed near the bottom of the chart should not have '1' on MSB and samples from the top shouldn't have '0' on the first bit.

Have you ever encounter problem like this? Have you any suggestion where to look? I really will appreciate any halp.

Configuration of Codec is the same as in example ("AIC31 drv") with the configuration. My mcasp configuration is below:

void mcasp_init()

{

//McASPGlobalCtlReset(CSL_DSP_MCASP3_CFG_REGS); //?? while? then set?

McASPTxReset(CSL_DSP_MCASP3_CFG_REGS);

McASPRxReset(CSL_DSP_MCASP3_CFG_REGS);

McASPTxFmtI2SSet(CSL_DSP_MCASP3_CFG_REGS,

32U,

32U,

MCASP_TX_MODE_NON_DMA);

McASPRxFmtI2SSet(CSL_DSP_MCASP3_CFG_REGS,

32U,

32U,

MCASP_RX_MODE_NON_DMA);

McASPTxFmtMaskSet(CSL_DSP_MCASP3_CFG_REGS,

0xFFFFFFFF);

McASPRxFmtMaskSet(CSL_DSP_MCASP3_CFG_REGS,

0xFFFFFFFF);

McASPTxFrameSyncCfg(CSL_DSP_MCASP3_CFG_REGS,

0x2, // 2 slots i2s

MCASP_TX_FS_WIDTH_WORD,

MCASP_TX_FS_INT_BEGIN_ON_FALL_EDGE);

McASPRxFrameSyncCfg(CSL_DSP_MCASP3_CFG_REGS,

0x2, // 2 slots i2s

MCASP_RX_FS_WIDTH_WORD,

MCASP_RX_FS_INT_BEGIN_ON_FALL_EDGE);

//tx clock

McASPTxClkCfg(CSL_DSP_MCASP3_CFG_REGS,

MCASP_TX_CLK_INTERNAL,

0x13, // HCLK /20 -> XCLK

0x7); // aux_clk / 8

McASPTxClkPolaritySet(CSL_DSP_MCASP3_CFG_REGS,

MCASP_TX_CLK_POL_RIS_EDGE); // 1 bit shifted so rising

McASPTxHFClkPolaritySet(CSL_DSP_MCASP3_CFG_REGS,

MCASP_TX_HI_FREQ_CLK_NO_INVERT);

//rx clock

McASPRxClkCfg(CSL_DSP_MCASP3_CFG_REGS,

MCASP_RX_CLK_INTERNAL,

0x13, // HCLK /20 -> RCLK

0x7); // aux_clk / 8

McASPRxClkPolaritySet(CSL_DSP_MCASP3_CFG_REGS,

MCASP_RX_CLK_POL_RIS_EDGE);

McASPRxHFClkPolaritySet(CSL_DSP_MCASP3_CFG_REGS,

MCASP_RX_HI_FREQ_CLK_NO_INVERT);

//sync -> so rx functions before are bypassed, on evm rx-clk pins are not present

McASPTxRxClkSyncEnable(CSL_DSP_MCASP3_CFG_REGS);

McASPTxTimeSlotSet(CSL_DSP_MCASP3_CFG_REGS,

0x3); //?? 2

McASPRxTimeSlotSet(CSL_DSP_MCASP3_CFG_REGS,

0x3); //?? 2

McASPSerializerTxSet(CSL_DSP_MCASP3_CFG_REGS,

0);

McASPSerializerRxSet(CSL_DSP_MCASP3_CFG_REGS,

1);

McASPPinMcASPSet(CSL_DSP_MCASP3_CFG_REGS,

MCASP_PIN_AXR(0) | MCASP_PIN_AXR(1) |

MCASP_PIN_AFSX |

MCASP_PIN_ACLKX); //??

McASPPinDirOutputSet(CSL_DSP_MCASP3_CFG_REGS,

MCASP_PIN_AXR(0) |

MCASP_PIN_AFSX |

MCASP_PIN_ACLKX);

McASPPinDirInputSet(CSL_DSP_MCASP3_CFG_REGS,

MCASP_PIN_AXR(1));

McASPTxClkStart(CSL_DSP_MCASP3_CFG_REGS,

MCASP_TX_CLK_INTERNAL);

McASPRxClkStart(CSL_DSP_MCASP3_CFG_REGS,

MCASP_RX_CLK_INTERNAL);

McASPTxIntEnable(CSL_DSP_MCASP3_CFG_REGS,

MCASP_TX_DATAREADY); // are you sure

//McASPTxIntEnable(CSL_DSP_MCASP3_CFG_REGS,

// MCASP_TX_DATAREADY); // are you sure

// clear serializers and status regs

McASPTxSerActivate(CSL_DSP_MCASP3_CFG_REGS);

McASPRxSerActivate(CSL_DSP_MCASP3_CFG_REGS);

// prevent overrun

McASPTxBufWrite(CSL_DSP_MCASP3_CFG_REGS,

0,

0x0);

while(McASPTxStatusGet(CSL_DSP_MCASP3_CFG_REGS) & MCASP_TX_STAT_DATAREADY);

// frame sync generator and state machines

McASPTxEnable(CSL_DSP_MCASP3_CFG_REGS);

McASPRxEnable(CSL_DSP_MCASP3_CFG_REGS);

}