Other Parts Discussed in Thread: SYSBIOS

Tool/software: TI-RTOS

Hello, TI Experts,

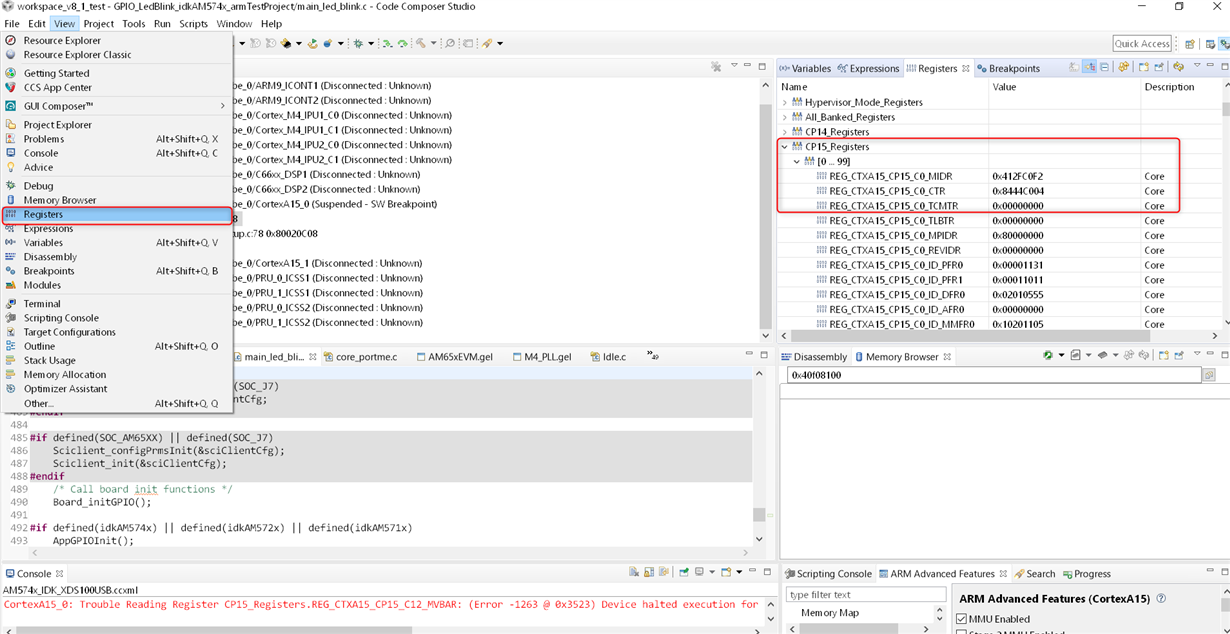

Our customer sent us questions about "MMU setting" with PROCESSOR-SDK-RTOS-AM57X.

They would like to know the recommended way of integrating multiple sample projects including driver software by referring to the MMU setting.

Question:

- Could you tell us the MMU setting policy of the sample project including driver software (for AM574x and AM335x)?

- Are there any fundamental rule or basic concept of those sample project including driver software?

- Could you tell us MMU setting policy of the each project including MAIRn registers setting?

Best regards,