Other Parts Discussed in Thread: AM3359

Tool/software: Linux

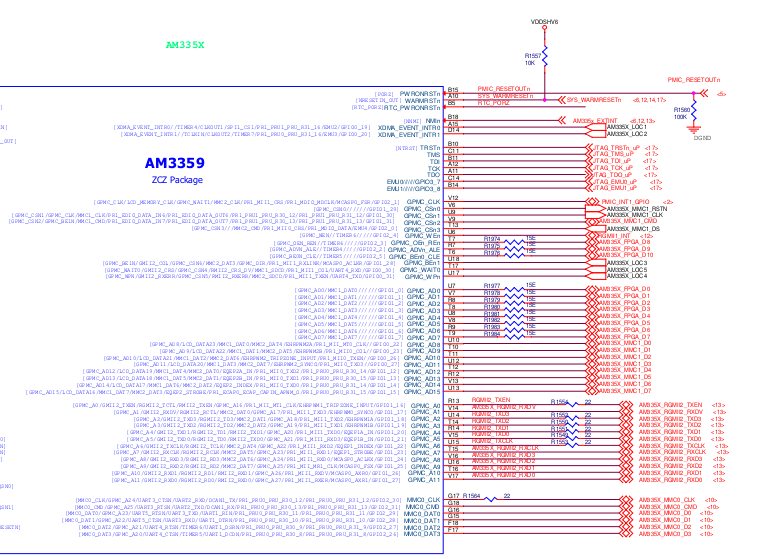

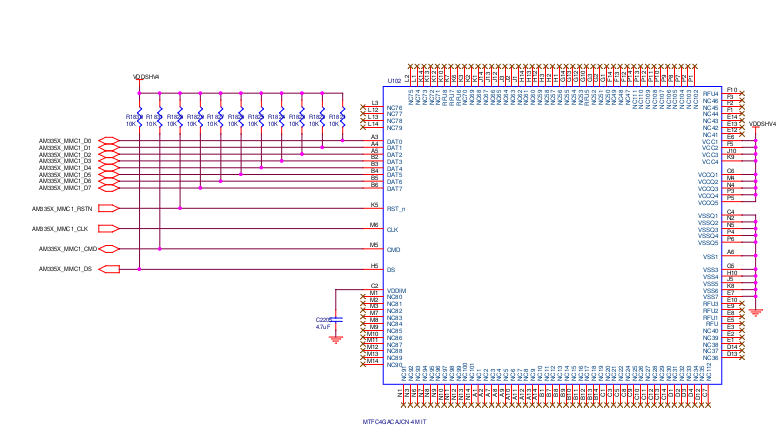

We are working on a board containing AM3359 processor.

SDK we are using is ti-processor-sdk-linux-am335x-evm-05.00.00.15.

Our customer wants to see the throughput of the data transfer between processor (AM3359) and FPGA connected through 8 GPMC lines using EDMA

As of now we've created a project in Code Composer Studio ( CCS ) with a GEL file and a C program & we are able to send data to FPGA through these 8 GPMC lines.

Right now we didn't insert any SD Card(i.e. Processor is not booted up).

Using JTAG & CCS only we did it.

Now we are not clear about how to proceed further in this regard on how to associate this gpmc program with EDMA protocol in Linux-SDK to send data to FPGA.

All we want now is to implement GPMC_EDMA data transfer program as per the below flow.

Processor booted ----> Run GPMC_EDMA Data transfer program ----> Complete data transfer ----> Calculate throughput.

Here is my code for transferring data to FPGA through 8 GPMC lines.

#include <stdio.h>

#define GPMC_BASE 0x50000000

#define GPMC_SYSCONFIG *( volatile unsigned int * )(GPMC_BASE + 0x010)

#define GPMC_SYSSTATUS *( volatile unsigned int * )(GPMC_BASE + 0x014)

#define GPMC_CONFIG *( volatile unsigned int * )(GPMC_BASE + 0x050)

#define GPMC_STATUS *( volatile unsigned int * )(GPMC_BASE + 0x054)

//Following are config registers for CS_0

#define GPMC_CONFIG1_0 *( volatile unsigned int * )(GPMC_BASE + 0x060)

#define GPMC_CONFIG2_0 *( volatile unsigned int * )(GPMC_BASE + 0x064) //CS settings

#define GPMC_CONFIG3_0 *( volatile unsigned int * )(GPMC_BASE + 0x068) //ADV settings

#define GPMC_CONFIG4_0 *( volatile unsigned int * )(GPMC_BASE + 0x06C) //OE settings

#define GPMC_CONFIG5_0 *( volatile unsigned int * )(GPMC_BASE + 0x070) //

#define GPMC_CONFIG6_0 *( volatile unsigned int * )(GPMC_BASE + 0x074) //

#define GPMC_CONFIG7_0 *( volatile unsigned int * )(GPMC_BASE + 0x078) //

#define PRCM_BASE 0x44E00000

#define CM_PER_GPMC_CLKCTRL *( volatile unsigned int * )(PRCM_BASE + 0x030)

#define BUF_SIZE 10

int main(void)

{

unsigned int i,j,k;

unsigned int buf[BUF_SIZE];

for(i=0;i<BUF_SIZE;i++){

buf[i]=i+1;

}

printf("Test GPMC memory Async 8 bit\n");

//CM_PER_GPMC_CLKCTRL = 0x2;

i = GPMC_CONFIG;

i = i | 2;

//GPMC_CONFIG = i; // We are not using any address bits.

//GPMC_CONFIG1_0 = 0x13;

GPMC_CONFIG2_0 = 0x61F10;//0x1F1F1F; // Highest delay - optimize this for speed.

GPMC_CONFIG3_0 = 0x77011F71;//0x771F1F7F; // Highest delay - optimize this for speed.

GPMC_CONFIG4_0 = 0x0501E77F;//0x1F0FE77F; // Highest delay - optimize this for speed.

GPMC_CONFIG5_0 = 0xF1F061F;//0xF1F1F1F; // Highest delay - optimize this for speed.

GPMC_CONFIG6_0 = 0x1F70F0F;//0x1F70F0F; // Highest delay - optimize this for speed.

GPMC_CONFIG7_0 = 0xF48; // CS0 starts at 0x08000000 and size is 16MB. First 0xFFFFF not available

#if 0

for(i=0; i < 1024; i+=2){

j = (0x08000000) ; //+i);

k = *(unsigned int *)j;

printf("0x%X\n", k );

}

#endif

int t=0;

while(1){

//count++;

// write to the same location - for oscilloscope probe of signals.

//printf("writing 0's\n");

//*(unsigned int *)(0x08000000) = 0x0;

printf("Sent %d bytes\n",BUF_SIZE);

for(i=0;i<BUF_SIZE;i++){

*(unsigned int *)(0x08000000) = buf[i];

}

//*(unsigned int *)(0x08000000) = buf[1];

/*if(t==0){

//*(unsigned int *)(0x08000000) = 0xA5;

*(unsigned int *)(0x08000000) = count;

t=1;

}

else if(t==1){

//*(unsigned int *)(0x08000000) = 0x5A;

*(unsigned int *)(0x08000000) = count;

t=0;

}*/

}

return 0;

}

Someone kindly help me to proceed further as we have a severe time restriction and also we are new to this one.

Thanks & Regards

Vamsi