Hello Community,

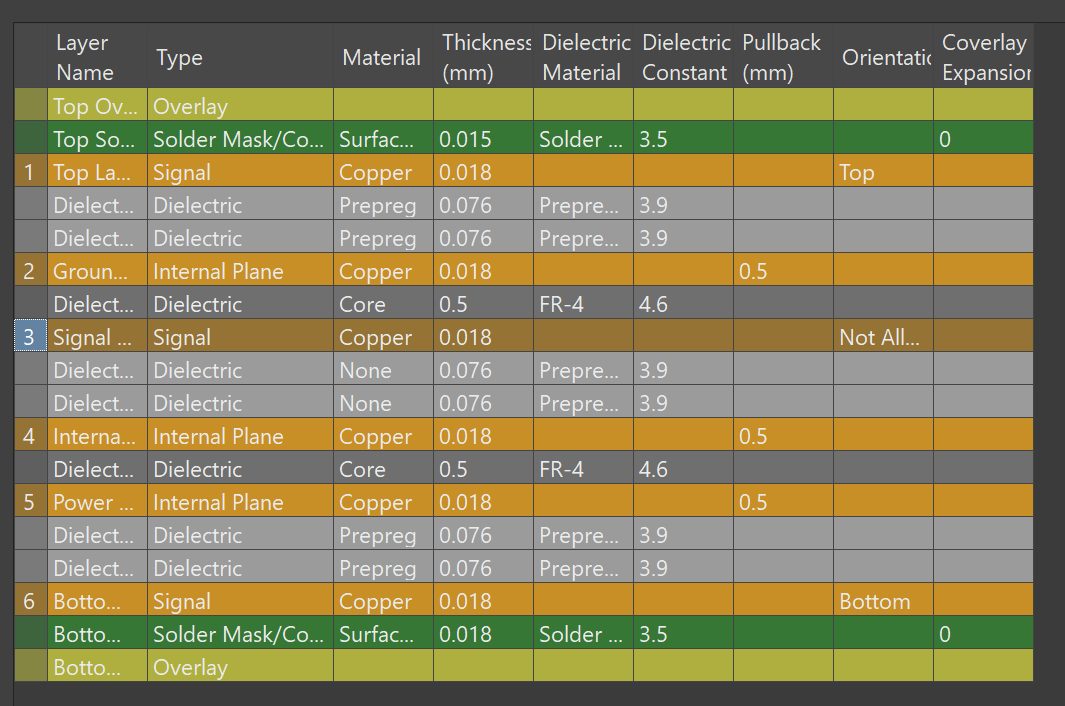

I have a board stack of 6 layers, some of which are fully filled planes (plane).

1. Tell me which plane (# 2 or # 4) in my situation is the reference for calculating the impedance for the conductors located on the inner layer (# 3)? And please explain why you think so.

2. Will the split plane, which is NOT a reference, affect the impedance of the adjacent layer?