Part Number: AM5718

Other Parts Discussed in Thread: TMDXIDK5718,

Tool/software: Linux

hi,

I am using EVM TMDXIDK5718. I wanted to try out usbboot. For this purpose I have modified USB1 from host to device mode.

I have configured sysboot pins to enable usbboot.

I have tried the steps provided in link

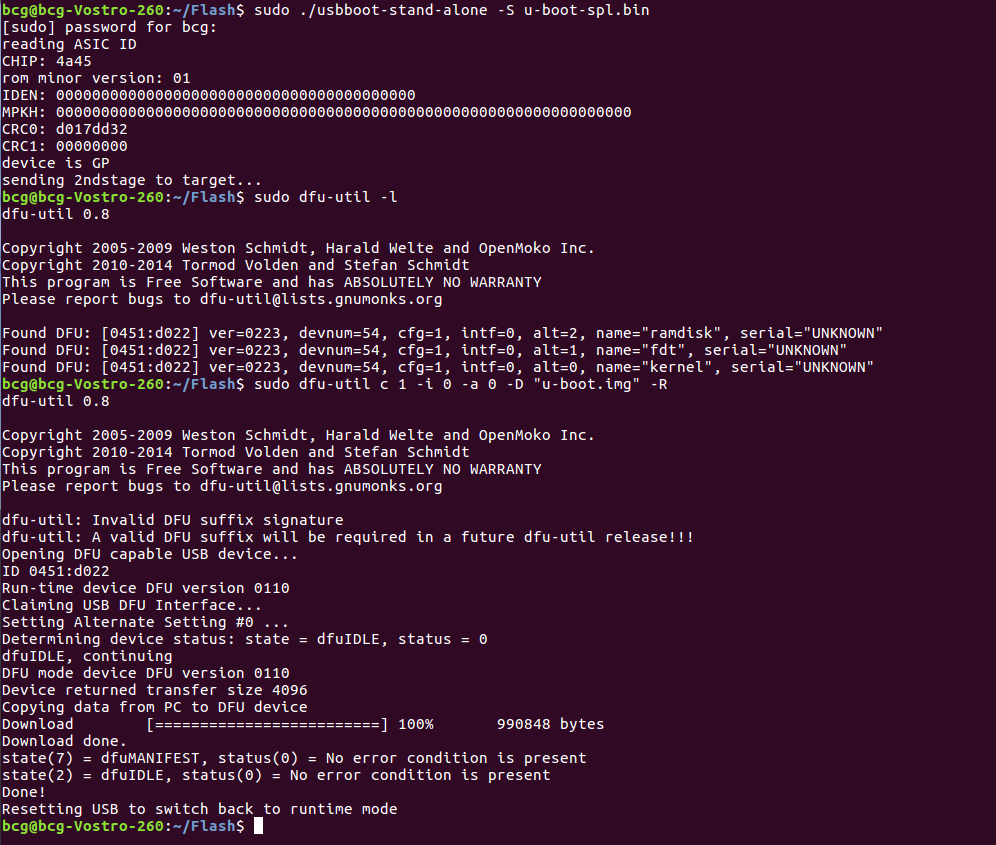

I could execute till following command "'host$ sudo usbboot-stand-alone -S spl/u-boot-spl.bin""

Here in I get the following response on minicom

""

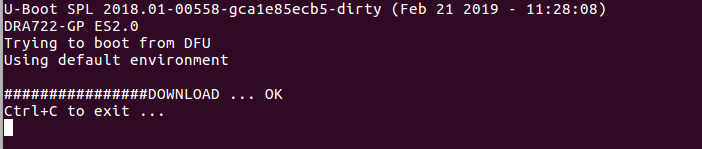

U-Boot SPL 2018.01-00558-gca1e85ecb5-dirty (Feb 18 2019 - 14:29:39)

DRA722-GP ES2.0

Trying to boot from DFU

Using default environment

port 0 can't be used as device

board usb init failed

""

AS i understand i could dump and execute usbspl to AM5718. But from there on these is no response.

What is the issue?? Why is usb init as device failing?? Pls respond