Tool/software: Code Composer Studio

Hi,

I want to run the No OS (Bare Metal) Example on the MINI5728.

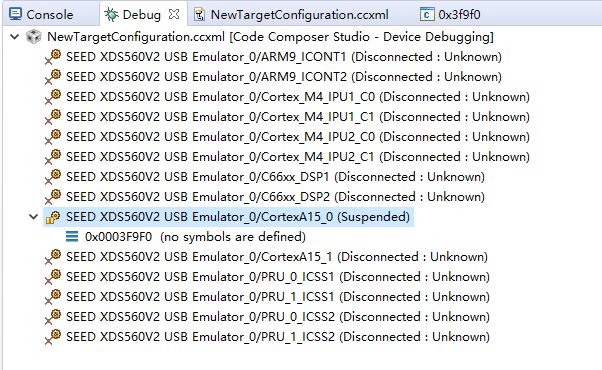

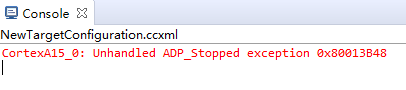

After I right click CortexA15_0 and select connect target., CCS prompts that Break at address "0x3f9f0" with no debug information available, or outside of program code.

Console prints the following information:

Cortex_M4_IPU1_C0: GEL Output: --->>> AM572x Cortex M4 Startup Sequence In Progress... <<<--- Cortex_M4_IPU1_C0: GEL Output: --->>> AM572x Cortex M4 Startup Sequence DONE! <<<--- Cortex_M4_IPU1_C1: GEL Output: --->>> AM572x Cortex M4 Startup Sequence In Progress... <<<--- Cortex_M4_IPU1_C1: GEL Output: --->>> AM572x Cortex M4 Startup Sequence DONE! <<<--- C66xx_DSP1: GEL Output: --->>> AM572x C66x DSP Startup Sequence In Progress... <<<--- C66xx_DSP1: GEL Output: --->>> AM572x C66x DSP Startup Sequence DONE! <<<--- C66xx_DSP2: GEL Output: --->>> AM572x C66x DSP Startup Sequence In Progress... <<<--- C66xx_DSP2: GEL Output: --->>> AM572x C66x DSP Startup Sequence DONE! <<<--- CortexA15_0: GEL Output: --->>> AM572x Cortex A15 Startup Sequence In Progress... <<<--- CortexA15_0: GEL Output: --->>> AM572x Cortex A15 Startup Sequence DONE! <<<--- CortexA15_1: GEL Output: --->>> AM572x Cortex A15 Startup Sequence In Progress... <<<--- CortexA15_1: GEL Output: --->>> AM572x Cortex A15 Startup Sequence DONE! <<<--- IcePick_D: GEL Output: Ipu RTOS is released from Wait-In-Reset. IcePick_D: GEL Output: Ipu SIMCOP is released from Wait-In-Reset. IcePick_D: GEL Output: IVAHD C66 is released from Wait-In-Reset. IcePick_D: GEL Output: IVAHD ICONT1 is released from Wait-In-Reset. IcePick_D: GEL Output: IVAHD ICONT2 is released from Wait-In-Reset. CS_DAP_DebugSS: GEL Output: --->>> CONFIGURE DEBUG DPLL settings to 1.9 GHZs <<<--- CS_DAP_DebugSS: GEL Output: > Setup DebugSS 1.9GHz in progress... CS_DAP_DebugSS: GEL Output: < Done with Setup DebugSS Trace export clock (TPIU) to 97MHz CS_DAP_DebugSS: GEL Output: < Done with Setup DebugSS PLL Clocking 1.9GHz CS_DAP_DebugSS: GEL Output: < Done with Setup DebugSS ATB Clocking 380MHz CS_DAP_DebugSS: GEL Output: < Done with Setup DebugSS Trace export clock (TPIU) to 97MHz CS_DAP_DebugSS: GEL Output: --->>> TURNING ON L3_INSTR and L3_3 clocks required for debug instrumention <<<<<<---- CS_DAP_DebugSS: GEL Output: ---<<< L3 instrumentation clocks are enabled >>>> --- CS_DAP_DebugSS: GEL Output: --->>> Mapping TIMER supsend sources to default cores <<<<<<---- CS_DAP_PC: GEL Output: Cortex-A15 1 is not in WIR mode so nothing to do. CortexA15_0: GEL Output: --->>> AM572x GP EVM <<<--- CortexA15_0: GEL Output: --->>> AM572x Target Connect Sequence Begins ... <<<--- CortexA15_0: GEL Output: --->>> I2C Init <<<--- CortexA15_0: GEL Output: --->>> AM572x Begin MMC2 Pad Configuration <<<--- CortexA15_0: GEL Output: --->>> AM572x End MMC2 Pad Configuration <<<--- CortexA15_0: GEL Output: --->>> AM572x PG1.1 GP device <<<--- CortexA15_0: GEL Output: --->>> PRCM Clock Configuration for OPPNOM in progress... <<<--- CortexA15_0: GEL Output: Cortex A15 DPLL OPP 0 clock config is in progress... CortexA15_0: GEL Output: Cortex A15 DPLL is already locked, now unlocking... CortexA15_0: GEL Output: Cortex A15 DPLL OPP 0 is DONE! CortexA15_0: GEL Output: IVA DPLL OPP 0 clock config is in progress... CortexA15_0: GEL Output: IVA DPLL OPP 0 is DONE! CortexA15_0: GEL Output: PER DPLL OPP 0 clock config in progress... CortexA15_0: GEL Output: PER DPLL already locked, now unlocking CortexA15_0: GEL Output: PER DPLL OPP 0 is DONE! CortexA15_0: GEL Output: CORE DPLL OPP 0 clock config is in progress... CortexA15_0: GEL Output: CORE DPLL OPP already locked, now unlocking.... CortexA15_0: GEL Output: CORE DPLL OPP 0 is DONE! CortexA15_0: GEL Output: ABE DPLL OPP 0 clock config in progress... CortexA15_0: GEL Output: ABE DPLL OPP 0 is DONE! CortexA15_0: GEL Output: GMAC DPLL OPP 0 clock config is in progress... CortexA15_0: GEL Output: GMAC DPLL OPP 0 is DONE! CortexA15_0: GEL Output: GPU DPLL OPP 0 clock config is in progress... CortexA15_0: GEL Output: GPU DPLL OPP 0 is DONE! CortexA15_0: GEL Output: DSP DPLL OPP 0 clock config is in progress... CortexA15_0: GEL Output: DSP DPLL OPP 0 is DONE! CortexA15_0: GEL Output: PCIE_REF DPLL OPP 0 clock config is in progress... CortexA15_0: GEL Output: PCIE_REF DPLL OPP 0 is DONE! CortexA15_0: GEL Output: --->>> PRCM Clock Configuration for OPP 0 is DONE! <<<--- CortexA15_0: GEL Output: --->>> PRCM Configuration for all modules in progress... <<<--- CortexA15_0: GEL Output: --->>> PRCM Configuration for all modules is DONE! <<<--- CortexA15_0: GEL Output: --->>> DDR3 Initialization is in progress ... <<<--- CortexA15_0: GEL Output: DDR DPLL clock config for 532MHz is in progress... CortexA15_0: GEL Output: DDR DPLL clock config for 532MHz is in DONE! CortexA15_0: GEL Output: Launch full leveling CortexA15_0: GEL Output: Updating slave ratios in PHY_STATUSx registers CortexA15_0: GEL Output: as per HW leveling output CortexA15_0: GEL Output: HW leveling is now disabled. Using slave ratios from CortexA15_0: GEL Output: PHY_STATUSx registers CortexA15_0: GEL Output: Launch full leveling CortexA15_0: GEL Output: Updating slave ratios in PHY_STATUSx registers CortexA15_0: GEL Output: as per HW leveling output CortexA15_0: GEL Output: HW leveling is now disabled. Using slave ratios from CortexA15_0: GEL Output: PHY_STATUSx registers CortexA15_0: GEL Output: Two EMIFs in interleaved mode - (2GB total) CortexA15_0: GEL Output: --->>> DDR3 Initialization is DONE! <<<--- CortexA15_0: GEL Output: --->>> Mapping TIMER suspend sources to default cores <<<<<<---- CortexA15_0: GEL Output: --->>> IPU1SS Initialization is in progress ... <<<--- CortexA15_0: GEL Output: --->>> IPU1SS Initialization is DONE! <<<--- CortexA15_0: GEL Output: --->>> IPU2SS Initialization is in progress ... <<<--- CortexA15_0: GEL Output: --->>> IPU2SS Initialization is DONE! <<<--- CortexA15_0: GEL Output: --->>> DSP1SS Initialization is in progress ... <<<--- CortexA15_0: GEL Output: DEBUG: Clock is active ... CortexA15_0: GEL Output: DEBUG: Checking for data integrity in DSPSS L2RAM ... CortexA15_0: GEL Output: DEBUG: Data integrity check in GEM L2RAM is sucessful! CortexA15_0: GEL Output: --->>> DSP1SS Initialization is DONE! <<<--- CortexA15_0: GEL Output: --->>> DSP2SS Initialization is in progress ... <<<--- CortexA15_0: GEL Output: DEBUG: Clock is active ... CortexA15_0: GEL Output: DEBUG: Checking for data integrity in DSPSS L2RAM ... CortexA15_0: GEL Output: DEBUG: Data integrity check in GEM L2RAM is sucessful! CortexA15_0: GEL Output: --->>> DSP2SS Initialization is DONE! <<<--- CortexA15_0: GEL Output: --->>> IVAHD Initialization is in progress ... <<<--- CortexA15_0: GEL Output: DEBUG: Clock is active ... CortexA15_0: GEL Output: --->>> IVAHD Initialization is DONE! ... <<<--- CortexA15_0: GEL Output: --->>> PRUSS 1 and 2 Initialization is in progress ... <<<--- CortexA15_0: GEL Output: --->>> PRUSS 1 and 2 Initialization is in complete ... <<<--- CortexA15_0: GEL Output: --->>> AM572x Target Connect Sequence DONE !!!!! <<<--- CortexA15_0: GEL Output: --->>> Mapping TIMER suspend sources to default cores <<<<<<---- CortexA15_0: GEL Output: --->>> IPU1SS Initialization is in progress ... <<<--- CortexA15_0: GEL Output: --->>> IPU1SS Initialization is DONE! <<<--- CortexA15_0: GEL Output: --->>> IPU2SS Initialization is in progress ... <<<--- CortexA15_0: GEL Output: --->>> IPU2SS Initialization is DONE! <<<--- CortexA15_0: GEL Output: --->>> DSP1SS Initialization is in progress ... <<<--- CortexA15_0: GEL Output: DEBUG: Clock is active ... CortexA15_0: GEL Output: DEBUG: Checking for data integrity in DSPSS L2RAM ... CortexA15_0: GEL Output: DEBUG: Data integrity check in GEM L2RAM is sucessful! CortexA15_0: GEL Output: --->>> DSP1SS Initialization is DONE! <<<--- CortexA15_0: GEL Output: --->>> DSP2SS Initialization is in progress ... <<<--- CortexA15_0: GEL Output: DEBUG: Clock is active ... CortexA15_0: GEL Output: DEBUG: Checking for data integrity in DSPSS L2RAM ... CortexA15_0: GEL Output: DEBUG: Data integrity check in GEM L2RAM is sucessful! CortexA15_0: GEL Output: --->>> DSP2SS Initialization is DONE! <<<--- CortexA15_0: GEL Output: --->>> IVAHD Initialization is in progress ... <<<--- CortexA15_0: GEL Output: DEBUG: Clock is active ... CortexA15_0: GEL Output: --->>> IVAHD Initialization is DONE! ... <<<--- CortexA15_0: GEL Output: --->>> PRUSS 1 and 2 Initialization is in progress ... <<<--- CortexA15_0: GEL Output: --->>> PRUSS 1 and 2 Initialization is in complete ... <<<---

How should I solve this problem?

Thank you!