Hi Friends,

I am using TMS320C6748 LCDK Dev Kit Rev A7A. I have using the starterware support from ti .On the example codes

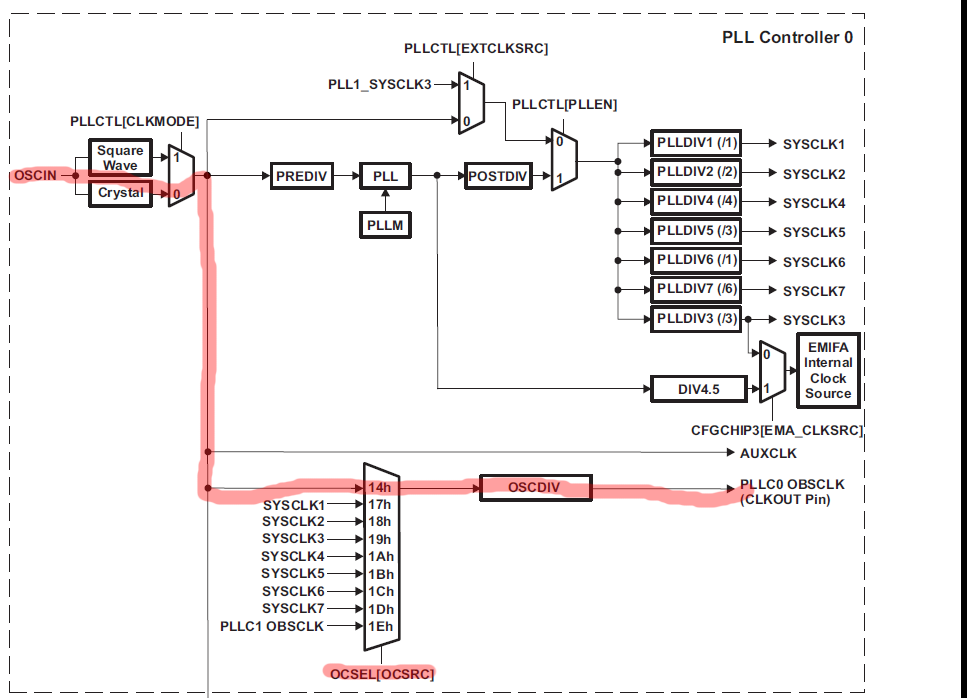

for clock PLL0 it is running by default with 300MHZ & PLL1 at 150MHZ as internal Oscilator is selected .

I am unable understand how the parameters like div,mul ,pre,post div are able config the clock for PLL0 and PLL1.

When I am trying see the clock by XCLKOUT pin by configuring as clock out pin it is showing only 24MHZ(which is external crystal frequency).

Can any one tell me the formulae applying on it & how much is internal oscillator frequency?

Regards,

Ashrumochan.