Tool/software: TI-RTOS

Hello, TI Experts,

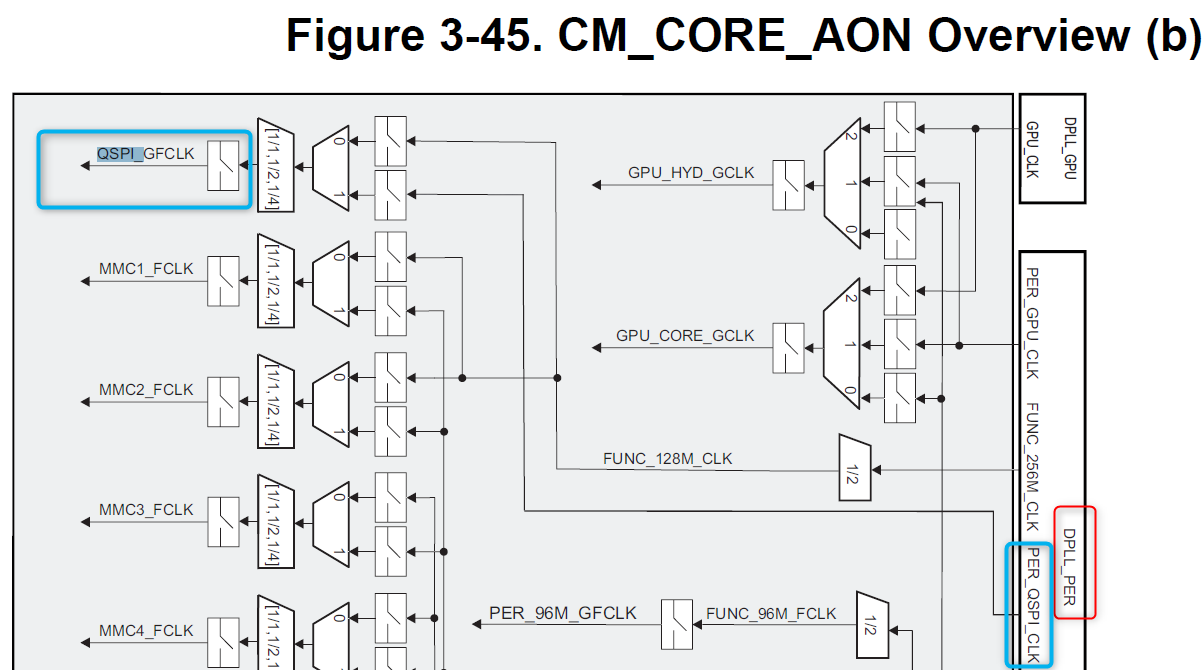

Our customer sent us questions about QSPI-Flash CLK with TMDXIDK5728.

They want to know how to change the QSPI-Flash CLK(SPIMEM_CLK in TMDXIDK5728 schematics).

We found related link like below;

http://processors.wiki.ti.com/index.php/Processor_SDK_RTOS_BOOT_AM57x#SBL_Customization

1: We tried to modify "spiParams.bitRate".

But QSPI-Flash CLK on the TMDXIDK5728 seems not to be changed.

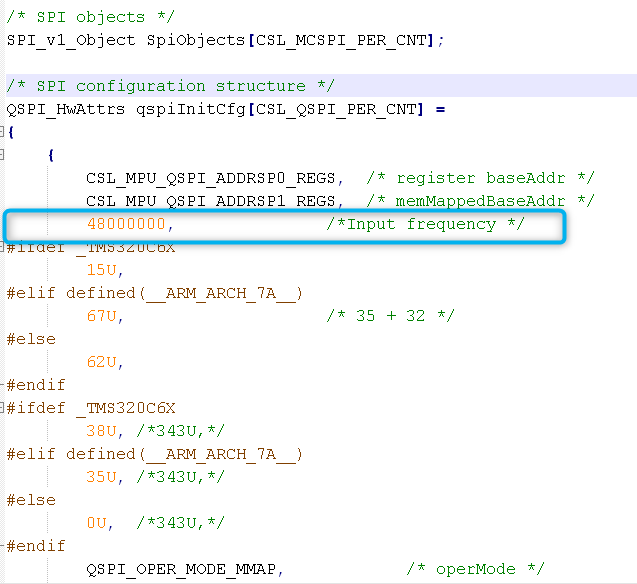

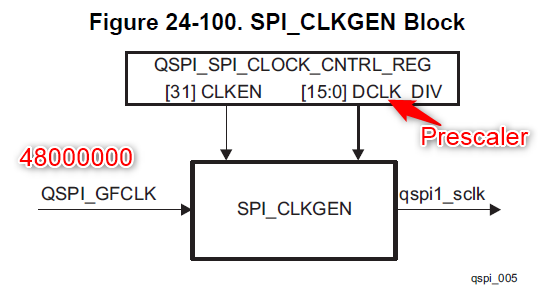

2: We found QSPI_HwAttrs parameter in C:\ti\pdk_am57xx_1_0_13\packages\ti\drv\spi\soc\QSPI_v1.h.

But we cannot find how to modify ”funcClk” in QSPI_v1.h.

Question:

Could you tell us recommended way of changing QSPI-Flash CLK with PROCESSOR-SDK-RTOS-AM57X?

- Which file should be modified?

- Which line of the file should be modified?

Best regards,