Other Parts Discussed in Thread: SYSBIOS

Dear TI team,

we're currently trying to figure out where to place our own application that is supposed to run on the R5F cores of a AM6548, and I have a few questions regarding the MSMC SRAM.

The linker script (ti\pdk_am65xx_1_0_3\packages\ti\build\am65xx\linker_r5_sysbios.lds) that comes with the RTOS SDK version 05.02 links most of the application to the MSMC RAM, but the MSMC memory is somewhat fragmented:

0x70000000 - 0x700EFFFF - MSMC3

0x700F0000 - 0x700FFFFF - MSMC3_DMSC (Reserved for DMSC according to comment)

0x70100000 - 0x701F1FFF - MSMC3_H

0x701F2000 - 0x701FFFFF - MSMC3_NOCACHE

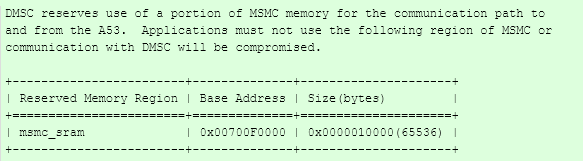

- What is the purpose of MSMC3_DMSC reserved area? I couldn't find that region anywhere in the documentation.

- I'm assuming that the MSMC3_NOCACHE region relies on a particular MPU configuration, but the r5_mpu.xs from the same folder doesn't seem to make that destinction, since there's only a single entry for the whole 0x70000000 area. What is the MSMC3_NOCACHE area supposed to be used for? Why does it need to be accessed uncached, if it is coherent, or rather with whom is it coherent?

- There's a r5_mpu.xs in ti\pdk_am65xx_1_0_3\packages\ti\drv\usb\example\bios\am65xx that contains a separate region for the 0x701F0000 - 0x701FFFFF region, but I believe there's a mistake in the sub-region mask, since a sub-region mask of 0x80 should disable that region for the LAST 1/8 of the range, instead of the FIRST 1/8 (not yet verified).

- The TRM talks about the 2 MB MSMC SRAM and that it's both a memory-mapped SRAM and a L3 cache, but I couldn't find a lot of information on that.

- Threre is the boardcfg_msmc structure with its msmc_cache_size field that is supposed to configure which fraction of the MSMC is used as a cache, and that defaults to 0x10 (* 1/32) which would equal one half of the MSMC used as a cache.

- There's also a MSMC_CACHE_CTRL register and its CACHE_SIZE field, and I'm guessing that this might be what boardcfg_msmc affects.

- Can you briefly describe what the MSMC SRAM ought to be used for, and what tradeoffs there are?

- With the default SCIClient initialization performed by the SBL, where the boardcfg pointer is NULL and thus the default gets used, can you tell me what the MSMC looks like to the R5F and to the A53?

Regards,

Dominic