Hi,

Here I got a problem when I enable Hyperlink, Mostly the Hyperlink can be enabled without error, but there is chance(about 1/150~200), it will find the following error status:

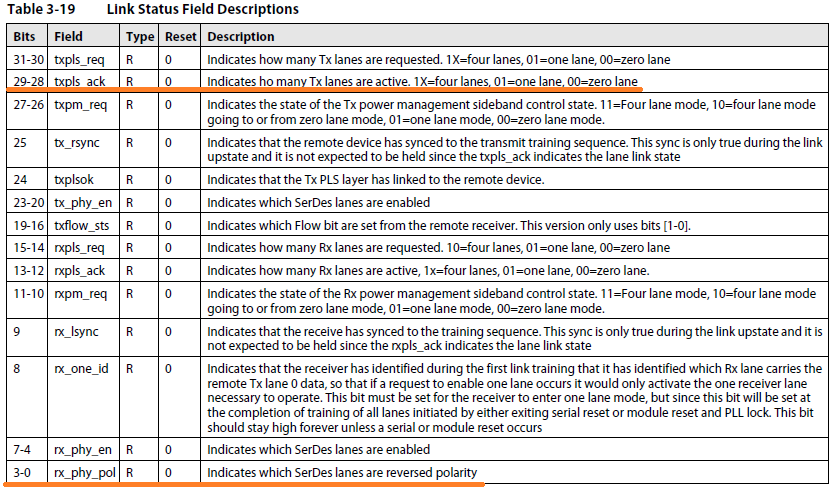

DSP1 hyperlink FAIL with link Status FDF00CF3, and ECC status: 0.

DSP2 hyperlink FAIL with link Status CCF0BDFB, and ECC status: 0.

While the correct status is:

DSP1 hyperlink successful with link Status FDF0BDFB, and ECC status: 0.

DSP2 hyperlink successful with link Status FDF0BDFB, and ECC status: 0.

As we can see, the error is due to the SerDes Lane plarity error which cause the link fail.

Since the Polarity is auto detect and set by Hyperlink module, may I know how can I handle the problem Or if there is an manual mode to set the polarity or not?

Thanks a lot.

B.R.

Jason