Other Parts Discussed in Thread: TPS65218D0

Tool/software: Code Composer Studio

The board that has been debugged successfully before, after rebuilding, there are the same problems as the following. Please help us to analyze them.

First AM4377 prints CC through serial port. After loading spl, it makes mistakes when running spl. Then we uses JTAG to locate errors. After loading spl, it runs step by step SPL to indicate errors as follows:

----------------

Texas Instruments XDS100v3 USB Debug Probe_0/CortexA9 (Suspended)

hang() at hang.c:26 0x402FD724

wait_for_lock(struct dpll_regs *)() at clock.c:47 0x402F46C0

do_setup_dpll(struct dpll_params *)() at clock.c:47 0x402F46C0 (next frame is identical to an existing frame)

------------------

static inline void wait_for_lock(const struct dpll_regs *dpll_regs)

{

if (!wait_on_value(ST_DPLL_CLK_MASK, ST_DPLL_CLK_MASK,

(void *)dpll_regs->cm_idlest_dpll, LDELAY)) {

printf("DPLL locking failed for 0x%x\n",

dpll_regs->cm_clkmode_dpll);

hang();

}

}

Follow the error prompt:dpll Locking failed.

The DPLL configuration is modified on the basis of the Ti gp_evm 1.5b development board. The specific configuration is as follows:

const struct dpll_params dpll_mpu = {600, 23, 1, -1, -1, -1, -1}; /* 24 MHz OPP 100*/

const struct dpll_params dpll_core = {1000, 23, -1, -1, 10, 8, 4}; /* 24 MHz */

const struct dpll_params dpll_per = {400, 9, 5, -1, -1, -1, -1}; /*{ 960, 23, 5, -1, -1, -1, -1}; ?*/

const struct dpll_params dpll_ddr = {50, 2, 1, -1, 2, -1, -1}; /*{ 400, 23, 1, -1, 1, -1, -1 };

On the hardware, we also carried out the following checks and tests:

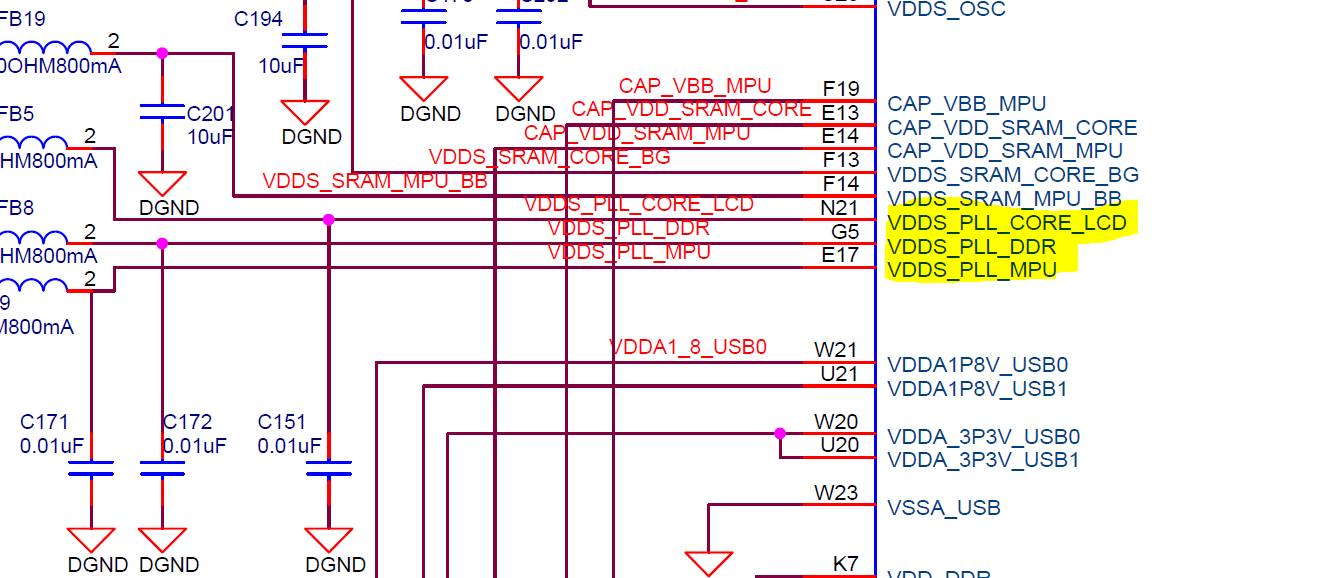

1、The output voltage of TPS65218D0 is OK;2、AM4377 reset signal is high level;3、The output of AM4377 external clock 24M is OK.

At present, it is impossible to locate where the problem lies.

Thanks & Best Regards,

Alex