Hi Experts,

My customer is using Radar SDK 3.04 with their algorithms/usecases. The executables work fine on TDA3x RVP with JTAG emulator. They tried "Load using QSPI and SD boot". But it stops at "Jumping to IPU1 CPU0 App".

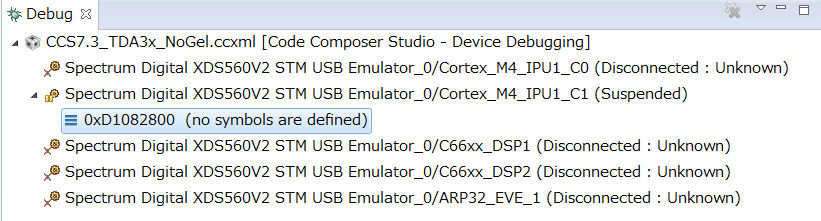

They put while loop at the begging of main function of IPU1_C1. The core doesn't come to the while loop, but it is at 0xD1082800 where the memory is not available as below.

Here are what they tried:

1. Original SDK 3.04 with QSPI and SD boot : It works fine.

2. 1 + their memory configuration modifications : It works fine.

3. 2 + their memory PDK and network modifications : It works fine.

4: 3 + their algorithms/usecases: It stops at "Jumping to IPU1 CPU0 App"

As our understanding, algorithms/usecases don't start after main. However the issue happens. Where and how should we check next?

From 3 to 4, AppImage size is almost twice (6MB to 12MB). Is there any possibility that the issue is related with the AppImage size?

Best regards,

Ken