Other Parts Discussed in Thread: TPS65217

Hello,

I have a custom board with an AM3358BZCZ100 using 2Gb DDR2. I try to boot from the SD-Card and I don't have an eMMC on my board. I have tested my DDR2 memory using CCS and JTAG and a GEL file which is working fine.

One out of 20 times I can see the SPL starting from the SD-Card when I switch on, when I remove the SD-Card every time when I power up I can see the 'C' character printing. I have to switch on the CPU first and then after that inserting the SD-Card, then the first stage bootloader is starting up. It will not go to the second stage bootloader..

I have created the SD-card using the ./create-sdcard.sh. I have 2 different 16Gb Class 10 SDHC micro sd cards.

I use SDK: ti-processor-sdk-linux-am335x-evm-05.03.00.07

When I load the MLO and U-Boot.img from the serial interface I mostly get the following output from the second stage bootloader (Without SD-Card inserted), then it hangs:

U-Boot 2018.01-00569-g7b4e473-dirty (Apr 13 2019 - 22:58:24 +0400)

CPU : AM335X-GP rev 2.1

Model: TI AM335x BeagleBone Black

DRAM: 256 MiB

NAND: 0 MiB

MMC:

And sometimes I get this result and then it hangs:

U-Boot 2018.01-00569-g7b4e473-dirty (Apr 13 2019 - 18:22:58 +0400)

CPU : AM335X-GP rev

2.1

Model: TI AM335x BeagleBone Black

DRAM: 256 MiB

NAND: 0 MiB

MMC: OMAP SD/MMC: 00, OMAP SD/MMC: 1

** Bad device mmc 0 **

Using default environment

When I start from SD-Card I get this (with #DEBUG active) :

U-Boot SPL 2018.01-00569-g7b4e473-dirty (Apr 14 2019 - 18:24:43)

omap24_i2c_findpsc: speed [kHz]: 100 psc: 0xb sscl: 0xd ssch: 0xf

Trying to boot from MMC1

uclass_find_device_by_seq: 0 0

- -1 -1 'omap_hsmmc'

- -1 -1 'omap_hsmmc'

- not found

uclass_find_device_by_seq: 1 0

- -1 -1 'omap_hsmmc'

- -1 -1 'omap_hsmmc'

- not found

malloc_simple: size=x, ptr=40, limit=68: 81f00028

malloc_simple: size=x, ptr=4, limit=6c: 81f00068

uclass_find_device_by_seq: 0 -1

uclass_find_device_by_seq: 0 0

- -1 -1 'omap_hsmmc'

- -1 -1 'omap_hsmmc'

- not found

malloc_simple: size=x, ptr=170, limit=1dc: 81f0006c

malloc_simple: size=x, ptr=40, limit=21c: 81f001dc

malloc_simple: size=x, ptr=4, limit=220: 81f0021c

uclass_find_device_by_seq: 0 -1

uclass_find_device_by_seq: 0 0

- -1 0 'omap_hsmmc'

- found

uclass_find_device_by_seq: 0 1

- -1 0 'omap_hsmmc'

- -1 -1 'omap_hsmmc'

- not found

malloc_simple: size=x, ptr=170, limit=390: 81f00220

My pin mux is as follow:

static struct module_pin_mux mmc0_pin_mux[] = {

{OFFSET(mmc0_dat3), (MODE(0) | RXACTIVE | PULLUP_EN)}, /* MMC0_DAT3 */

{OFFSET(mmc0_dat2), (MODE(0) | RXACTIVE | PULLUP_EN)}, /* MMC0_DAT2 */

{OFFSET(mmc0_dat1), (MODE(0) | RXACTIVE | PULLUP_EN)}, /* MMC0_DAT1 */

{OFFSET(mmc0_dat0), (MODE(0) | RXACTIVE | PULLUP_EN)}, /* MMC0_DAT0 */

{OFFSET(mmc0_clk), (MODE(0) | RXACTIVE | PULLUP_EN)}, /* MMC0_CLK */

{OFFSET(mmc0_cmd), (MODE(0) | RXACTIVE | PULLUP_EN)}, /* MMC0_CMD */

{OFFSET(mcasp0_aclkr), (MODE(4) | RXACTIVE)}, /* MMC0_WP */

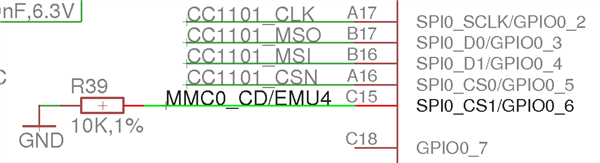

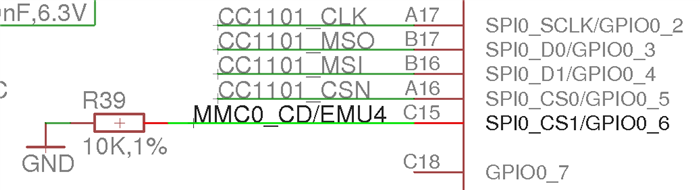

{OFFSET(spi0_cs1), (MODE(7) | RXACTIVE | PULLUP_EN)}, /* GPIO0_6 */

{-1},

};

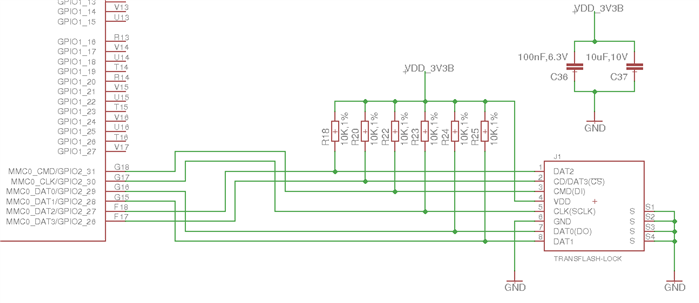

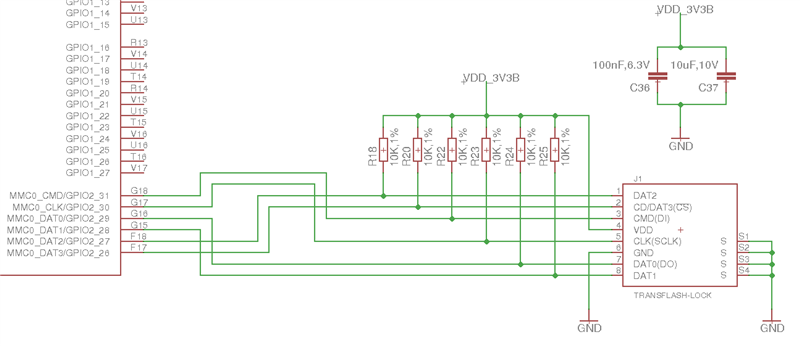

Here is the picture from the drawing that I copied from BBB. Only difference is that I don't have a separate CD pin on my SD-card connector connected:

Anyone has a clue why I get stuck?

Thanks in advance.