Other Parts Discussed in Thread: SYSBIOS

Tool/software: TI-RTOS

Hey,

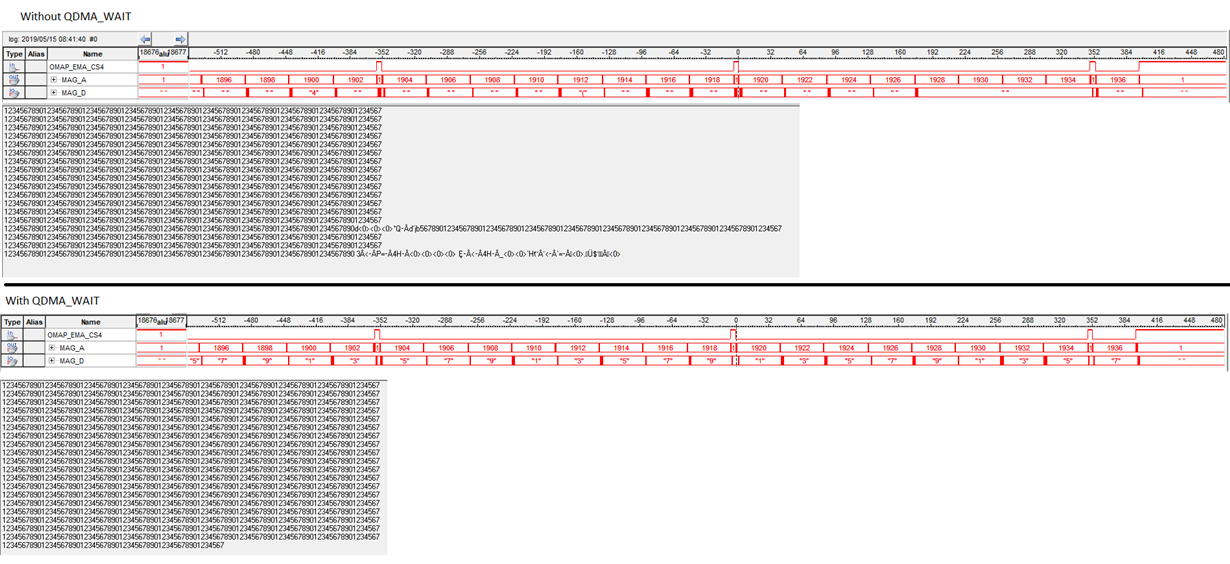

I am using QDMA to send data using EMIF. My problem is that with long words > 1950B, the last data is destroyed (with all the words everything is transmitted correctly). I noticed a similar problem when writing files to an SD card using EDMA. In my project cache memory is disabled. Can this be the cause of the problem? It doesn't use any functions in the project to flush cache memory, etc.

Please help.

Regards, Patryk.