Part Number: TMS320C6678

Hi,

How to calculate DDR3 clock speed?

I noticed CLK = CLKIN × ((PLLM+1) ÷ ((OUTPUT_DIVIDE+1) × (PLLD+1))) from datasheet section 2.5.4. So we can use that equation to calculate DDR3 clock speed right? I concluded from GEL file.

pdk_c667x_2_0_11\packages\ti\platform\evmc6678l

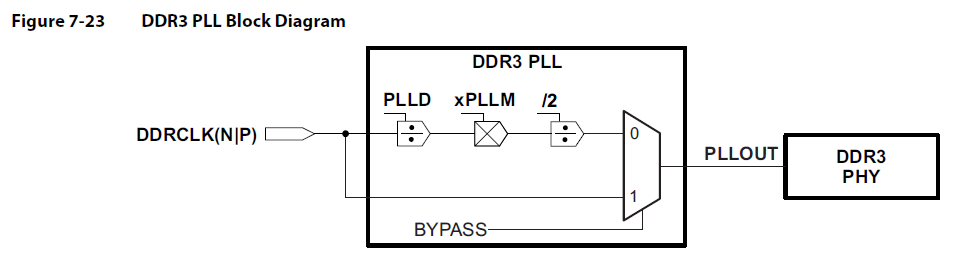

What i am confused is that the figure 7-23 in datasheet in which there is no need to add 1 with PLLM and PLLD. Please help to analyze in detail.

By the way, what's VCO?