Other Parts Discussed in Thread: SEGGER,

Tool/software: Linux

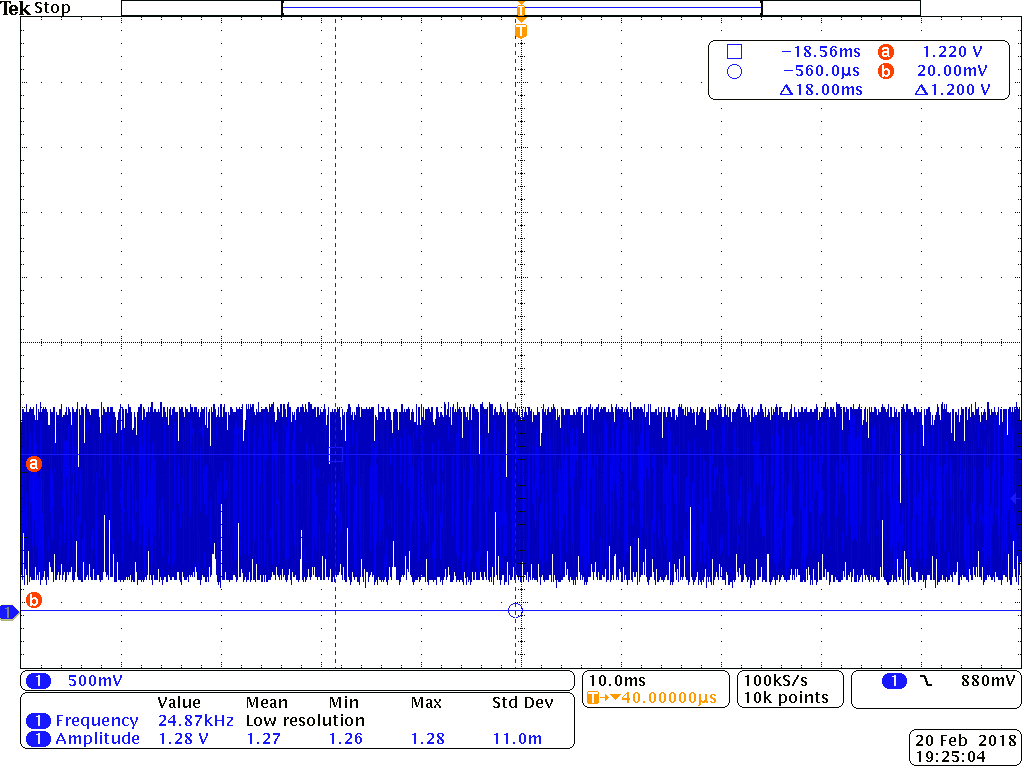

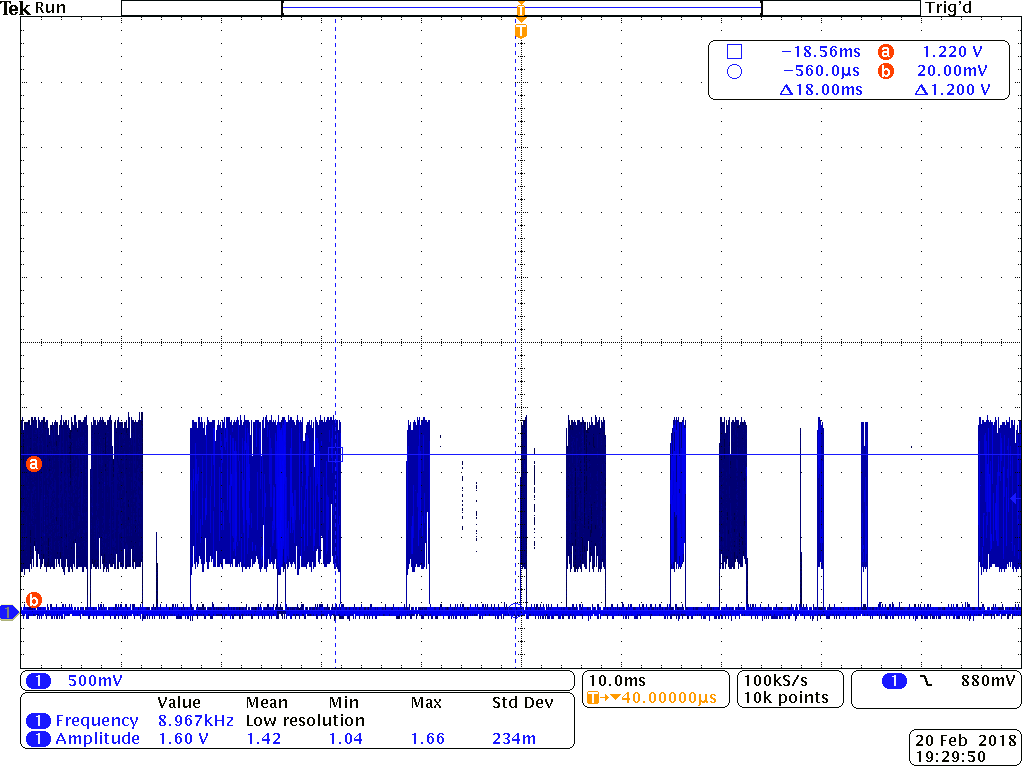

We've had a design in the field for 3 years that exhibits a 'slow' boot condition during which normal execution occurs at maybe 1/20 of the expected speed. It occurs on less than 1/10 of a percent of fielded units. It's slow enough where the WDT fires and creates a WDT reset event. However, the slow boot condition continues and the cycle repeats.. forever, until POR. Our work around has been to check the reset reason in u-boot and issue a reset from the PMIC if the reset reason is WDT. This resolves the issue and the device is able to boot normally after initially failing. However, the over all boot time is creating problems and we need to understand why this is occurring and what more can be done to avoid the situation, what is root cause? In one unit that that we've been able to capture the condition it seems to be related to CKE on the SDRAM. During a normal boot CKE show continuous clocking, however in the 'slow boot' condition CKE operates in a busting manner. See below. This design was reviewed 3 years ago by TI and a Hyperlynx simulation was performed on the SDRAM to ensure proper timing. This issue doesn't seem to be related to any environmental condition or any unusual electrical condition such as EMI or ESD.