Part Number: TDA3EVM , Custom Board

Tool/software: TI-RTOS

hi,

My SDK : PROCESSOR_SDK_VISION_03_04_00_00

I burn Qspi SBL OPP HIGH

An error occurred while running the app

OPP_OD and OPP_NOM are all running normally

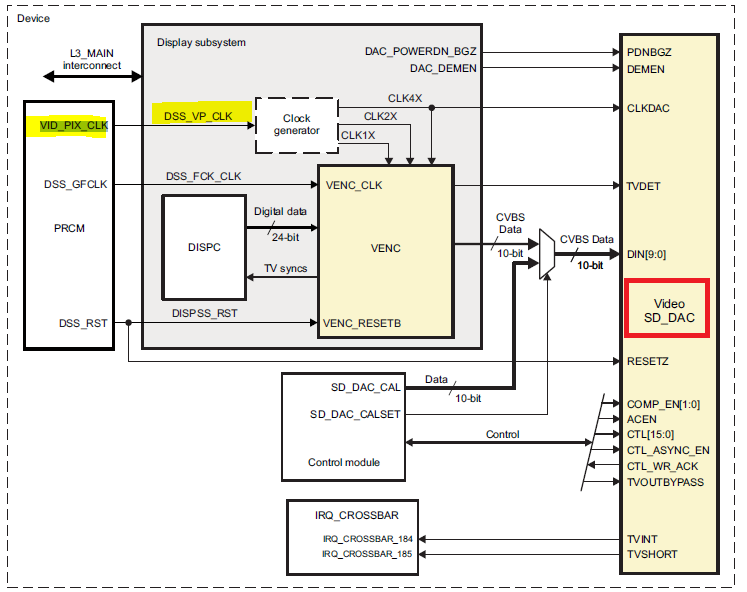

I guess it is ERROR because VID_PIX_CLK changed.

TDA3xx SBL Boot _zk190528_0 Identified 15X15 Silicon DPLL Configuration Completed Clock Domain Configuration Completed Module Enable Configuration Completed TI EVM PAD Configuration Completed DDR Configuration Completed TDA3xx SOC Init Completed App Image Download Begins Manufacturer ID - 0x9d Device ID - 0x18 IPU1 CPU0 Image Load Completed IPU1 CPU1 Image Load Completed DSP1 Image Load Completed App Image Download Completed EVE MMU configuration completed ***************************************************************** 32K Timer is used to measure cycles, divide by 32K to get time in seconds Reset to SBL Init Cycles - 342 (10.43 ms) SBL Initial Config Cycles - 210 (6.40 ms) SOC Init Cycles - 471 (14.37 ms) DDR Config Clock Cycles - 229 (6.98 ms) App Image Load Cycles - 6609 (201.69 ms) Slave Core Bootup Cycles - 112 (3.41 ms) SBL Boot-up Cycles - 7634 (232.97 ms) Time at which SBL started IPU1_0 - 7976 (243.40 ms) ***************************************************************** Jumping to IPU1 CPU1 App Jumping to IPU1 CPU0 App [IPU1-0] 0.303422 s: ***** IPU1_0 Firmware build time 17:12:24 May 30 2019 [IPU1-0] 0.303574 s: *** SYSTEM: CPU Frequency <ORG = 212800000 Hz>, <NEW = 212800000 Hz> [IPU1-0] 0.312114 s: SYSTEM: Notify register to [IPU1-1] line 0, event 15... [IPU1-0] 0.312267 s: SYSTEM: Notify register to [DSP1] line 0, event 15... [IPU1-0] 0.312572 s: *** UTILS: CPU MHz = 20 Mhz *** [IPU1-0] 0.312724 s: SYSTEM: System Common Init in progress !!! [IPU1-0] 0.321082 s: UTILS: CIO: Init Done !!! [IPU1-0] 0.321173 s: SYSTEM: IPC init in progress !!! [IPU1-0] 0.321234 s: SYSTEM: Notify init done !!! [IPU1-0] 0.321448 s: SYSTEM: MsgQ init done !!! [IPU1-0] 0.321539 s: SYSTEM: IPC init DONE !!! [IPU1-0] 0.323796 s: SYSTEM: System Common Init Done !!! [IPU1-0] 0.323888 s: SYSTEM: System Init in progress !!! [IPU1-0] 0.323949 s: SYSTEM: BSP Common Init in progress !!! [IPU1-0] 0.324071 s: SYSTEM: BSP Common Init Done !!! [IPU1-0] 0.324132 s: SYSTEM: BSP Platform Init in progress !!! [IPU1-0] 0.324284 s: PLATFORM: UNKNOWN CPU detected, defaulting to CPU REV 2.0 [IPU1-0] 0.324376 s: SYSTEM: BSP Platform Init Done !!! [IPU1-0] 0.324437 s: SYSTEM: FVID2 Init in progress !!! [IPU1-0] 0.324589 s: SYSTEM: FVID2 Init Done !!! [IPU1-0] 0.324650 s: SYSTEM: VPS Init in progress !!! [IPU1-0] 0.324711 s: SYSTEM: VPDMA Descriptor Memory Address translation ENABLED [0xa0000000 -> 0x80000000] [IPU1-0] 0.327151 s: *** VPDMA Firmware Loading... *** [IPU1-0] 0.327243 s: VPDMA Firmware Address = 0x9ffc7800 [IPU1-0] 0.327334 s: VPDMA Load Address = 0x4897d004 [IPU1-0] 0.327456 s: VPDMA Firmware Version = 0x4d0001b8 [IPU1-0] 0.327548 s: VPDMA List Busy Status = 0x00000000 [IPU1-0] 0.327609 s: *** VPDMA Firmware Load Success *** [IPU1-0] 0.362105 s: SYSTEM: VPS Init Done !!! [IPU1-0] 0.362837 s: UTILS: DMA: HWI Create for INT34 !!! [IPU1-0] 0.363173 s: SYSTEM: SW Message Box Msg Pool, Free Msg Count = 1024 [IPU1-0] 0.363295 s: SYSTEM: Heap = LOCAL_DDR @ 0x00000000, Total size = 262144 B (256 KB), Free size = 259120 B (253 KB) [IPU1-0] 0.363478 s: SYSTEM: Heap = SR_OCMC @ 0x00000000, Total size = 0 B (0 KB), Free size = 0 B (0 KB) [IPU1-0] 0.363630 s: SYSTEM: Heap = SR_DDR_CACHED @ 0x85703000, Total size = 369086464 B (351 MB), Free size = 369086464 B (351 MB) [IPU1-0] 0.363844 s: SYSTEM: Heap = SR_DDR_NON_CACHED @ 0xbfe00000, Total size = 915968 B (0 MB), Free size = 913664 B (0 MB) [IPU1-0] 0.364057 s: SYSTEM: Initializing Links !!! [IPU1-0] 0.445464 s: SYSTEM: Initializing Links ... DONE !!! [IPU1-0] 0.451595 s: BOARD: Board Init in progress !!! [IPU1-0] 0.451930 s: BOARD: Board Init Done !!! [IPU1-0] 0.460104 s: [IPU1-0] 0.460165 s: Vision SDK Version : [REL_VISION_SDK_03_04_00_00] [IPU1-0] 0.460257 s: FVID2 Version : [FVID_02_01_00_01] [IPU1-0] 0.460318 s: BSP Version : [PDK_01_10_00_xx] [IPU1-0] 0.460379 s: Platform : [EVM] [IPU1-0] 0.460440 s: SOC : [TDA3XX] [IPU1-0] 0.460501 s: SOC Revision : [ES2.0] [IPU1-0] 0.460531 s: Board Detected : [UNKNOWN] [IPU1-0] 0.461934 s: [IPU1-0] 0.462239 s: i2cMdSubmitChan: i2c0 transfer to slave address 0x51 failed [IPU1-0] 0.462331 s: src/bsp_deviceI2c.c @ Line 667: [IPU1-0] 0.462422 s: I2C0: DEV 0x51: ERROR !!! [IPU1-0] 0.462483 s: src/bsp_deviceI2c.c @ Line 689: [IPU1-0] 0.462575 s: I2C0: Error timeout 0 ms!!! [IPU1-0] 0.467089 s: [IPU1-0] 0.467364 s: i2cMdSubmitChan: i2c0 transfer to slave address 0x51 failed [IPU1-0] 0.467455 s: src/bsp_deviceI2c.c @ Line 478: [IPU1-0] 0.467516 s: I2C0: DEV 0x51: RD ERROR !!! [IPU1-0] 0.467608 s: src/bsp_deviceI2c.c @ Line 504: [IPU1-0] 0.467669 s: I2C0: Error timeout 0 ms!!! [IPU1-0] 0.467760 s: src/bsp_boardTda3xx.c @ Line 572: [IPU1-0] 0.467821 s: EEPROM read failed!! [IPU1-0] 0.467852 s: Base Board Revision : [REV A] [IPU1-0] 0.467913 s: Daughter Card Revision: [REV A] [IPU1-0] 0.468004 s: [IPU1-0] 0.469072 s: SYSTEM: UART: INTERRUPT Mode is Selected [IPU1-1] 0.310803 s: ***** IPU1_1 Firmware build time 17:10:46 May 30 2019 [IPU1-1] 0.310986 s: *** SYSTEM: CPU Frequency <ORG = 212800000 Hz>, <NEW = 212800000 Hz> [IPU1-1] 0.312419 s: SYSTEM: Notify register to [IPU1-0] line 0, event 15... [IPU1-1] 0.312572 s: SYSTEM: Notify register to [DSP1] line 0, event 15... [IPU1-1] 0.312999 s: SYSTEM: System Common Init in progress !!! [IPU1-1] 0.313853 s: UTILS: CIO: Init Done !!! [IPU1-1] 0.313944 s: SYSTEM: IPC init in progress !!! [IPU1-1] 0.314066 s: SYSTEM: Notify init done !!! [IPU1-1] 0.314249 s: SYSTEM: MsgQ init done !!! [IPU1-1] 0.314310 s: SYSTEM: IPC init DONE !!! [IPU1-1] 0.316324 s: SYSTEM: System Common Init Done !!! [IPU1-1] 0.316385 s: SYSTEM: System IPU1_1 Init in progress !!! [IPU1-1] 0.317147 s: UTILS: DMA: HWI Create for INT25 !!! [IPU1-1] 0.317330 s: SYSTEM: SW Message Box Msg Pool, Free Msg Count = 1024 [IPU1-1] 0.317422 s: SYSTEM: Heap = LOCAL_DDR @ 0x00000000, Total size = 262144 B (256 KB), Free size = 259296 B (253 KB) [IPU1-1] 0.317574 s: SYSTEM: Initializing Links !!! [IPU1-1] 0.362197 s: UTILS: PRF: ##### Cannot allocate Object for SYNC1 #### [IPU1-1] 0.363539 s: UTILS: PRF: ##### Cannot allocate Object for SYNC2 #### [IPU1-1] 0.365155 s: UTILS: PRF: ##### Cannot allocate Object for SYNC3 #### [IPU1-1] 0.366863 s: UTILS: PRF: ##### Cannot allocate Object for ALGORITHM0 #### [IPU1-1] 0.368754 s: UTILS: PRF: ##### Cannot allocate Object for ALGORITHM1 #### [IPU1-1] 0.370432 s: UTILS: PRF: ##### Cannot allocate Object for ALGORITHM2 #### [IPU1-1] 0.372110 s: UTILS: PRF: ##### Cannot allocate Object for ALGORITHM3 #### [IPU1-1] 0.373940 s: UTILS: PRF: ##### Cannot allocate Object for ALGORITHM4 #### [IPU1-1] 0.375770 s: UTILS: PRF: ##### Cannot allocate Object for ALGORITHM5 #### [IPU1-1] 0.377661 s: UTILS: PRF: ##### Cannot allocate Object for ALGORITHM6 #### [IPU1-1] 0.379643 s: UTILS: PRF: ##### Cannot allocate Object for ALGORITHM7 #### [IPU1-1] 0.379765 s: SYSTEM: Initializing Links ... DONE !!! [IPU1-1] 0.380223 s: UTILS: PRF: ##### Cannot allocate Object for DCANRX #### [IPU1-1] 0.380863 s: UTILS: PRF: ##### Cannot allocate Object for DCANTX #### [IPU1-1] 0.382785 s: UTILS: PRF: ##### Cannot allocate Object for zk_NULL0 #### [IPU1-1] 0.384706 s: UTILS: PRF: ##### Cannot allocate Object for zk_NULL1 #### [IPU1-1] 0.386719 s: UTILS: PRF: ##### Cannot allocate Object for zk_NULL2 #### [IPU1-1] 0.386811 s: SYSTEM: System IPU1_1 Init Done !!! [DSP1 ] 0.312419 s: SYSTEM: Notify register to [IPU1-0] line 0, event 15... [DSP1 ] 0.312450 s: SYSTEM: Notify register to [IPU1-1] line 0, event 15... [DSP1 ] 0.312541 s: ################ DSP1 clock = 730000000 [DSP1 ] 0.312572 s: *** UTILS: CPU MHz = 20 Mhz *** [DSP1 ] 0.312602 s: SYSTEM: System Common Init in progress !!! [DSP1 ] 0.312755 s: UTILS: CIO: Init Done !!! [DSP1 ] 0.312755 s: SYSTEM: IPC init in progress !!! [DSP1 ] 0.312785 s: SYSTEM: Notify init done !!! [DSP1 ] 0.312846 s: SYSTEM: MsgQ init done !!! [DSP1 ] 0.312846 s: SYSTEM: IPC init DONE !!! [DSP1 ] 0.313365 s: SYSTEM: System Common Init Done !!! [DSP1 ] 0.313395 s: SYSTEM: System DSP Init in progress !!! [DSP1 ] 0.313548 s: SYSTEM: SW Message Box Msg Pool, Free Msg Count = 1024 [DSP1 ] 0.313578 s: SYSTEM: Heap = LOCAL_L2 @ 0x00800000, Total size = 227264 B (221 KB), Free size = 227264 B (221 KB) [DSP1 ] 0.313639 s: SYSTEM: Heap = LOCAL_DDR @ 0x00000000, Total size = 524288 B (512 KB), Free size = 521432 B (509 KB) [DSP1 ] 0.313670 s: SYSTEM: Initializing Links !!! [DSP1 ] 0.318520 s: SYSTEM: Initializing Links ... DONE !!! [DSP1 ] 0.318550 s: SYSTEM: System DSP Init Done !!! [DSP1 ] 0.451595 s: SYSTEM: CACHE: L1P = 32 KB, L1D = 32 KB, L2 = 32 KB ... after boot !!! [DSP1 ] 0.451625 s: SYSTEM: CACHE: L1P = 32 KB, L1D = 32 KB, L2 = 32 KB ... after update by APP !!! [IPU1-0] 1.469133 s: [IPU1-0] 1.469438 s: i2cMdSubmitChan: i2c0 transfer to slave address 0x59 failed [IPU1-0] 1.469529 s: src/bsp_deviceI2c.c @ Line 346: [IPU1-0] 1.469621 s: I2C0: DEV 0x59: RD 0x4f ... ERROR !!! [IPU1-0] 1.469712 s: src/bsp_deviceI2c.c @ Line 412: [IPU1-0] 1.469773 s: I2C0: Error timeout 0 ms!!! [IPU1-0] 1.472518 s: QSPI Init Started [IPU1-0] 1.472671 s: MID - 9d [IPU1-0] 1.472732 s: DID - 18 [IPU1-0] 1.472762 s: QSPI Init Completed Sucessfully [IPU1-0] 1.480265 s: UTILS: DMM: API NOT supported in TDA3xx !!! [IPU1-0] 1.480357 s: UTILS: DMM: API NOT supported in TDA3xx !!! [IPU1-0] 1.481211 s: [IPU1-0] 1.481272 s: Current System Settings, [IPU1-0] 1.481302 s: ======================== [IPU1-0] 1.481363 s: Display Type : HDMI 1920x1080 @ 60fps [IPU1-0] 1.481424 s: Capture Source : Sensor OV10635 1280x720 @ 30fps - VIP, YUV422 [IPU1-0] 1.481516 s: My IP address : none [IPU1-0] 1.481547 s: ISS Settings : LDC=[OFF] VTNF=[OFF] WDR=[OFF] [IPU1-0] 1.481638 s: [IPU1-0] 1.481669 s: ============ [IPU1-0] 1.481699 s: Usecase Menu [IPU1-0] 1.481730 s: ============ [IPU1-0] 1.481791 s: [IPU1-0] [IPU1-0] Vision SDK Usecases, [IPU1-0] -------------------- [IPU1-0] 1: Single Camera Usecases [IPU1-0] 2: Multi-Camera LVDS Usecases [IPU1-0] 3: AVB RX Usecases, (TDA2x & TDA2Ex ONLY) [IPU1-0] 4: Dual Display Usecases, (TDA2x EVM ONLY) [IPU1-0] 5: ISS Usecases, (TDA3x ONLY) [IPU1-0] 6: TDA2x Stereo Usecases [IPU1-0] 9: RADAR Usecases [IPU1-0] a: Miscellaneous test's [IPU1-0] f: TIDL Usecase [IPU1-0] g: Camera Radar Combo Usecases [IPU1-0] [IPU1-0] s: System Settings [IPU1-0] [IPU1-0] x: Exit [IPU1-0] [IPU1-0] Enter Choice: [IPU1-0] [IPU1-0] 1.482126 s: [IPU1-0] 1.482492 s: [IPU1-0] [IPU1-0] Multi-Camera LVDS Usecases [IPU1-0] ---------------------------- [IPU1-0] 7: OV10635 & UB964 4CH CSI2 Capture + Display [IPU1-0] 8: OV10635 & UB964 4CH CSI2 Surround View (DSP) + Display (HDMI) [IPU1-0] [IPU1-0] x: Exit [IPU1-0] [IPU1-0] Enter Choice: [IPU1-0] [IPU1-0] 1.482706 s: [IPU1-0] Camera Selected or Number of LVDS Channels or Display is not 1080P60, Please try again [IPU1-0] 1.482919 s: [IPU1-0] 1.483194 s: i2cMdSubmitChan: i2c1 transfer to slave address 0x3d failed [IPU1-0] 1.483316 s: src/bsp_deviceI2c.c @ Line 346: [IPU1-0] 1.483407 s: I2C1: DEV 0x3d: RD 0xf5 ... ERROR !!! [IPU1-0] 1.483499 s: src/bsp_deviceI2c.c @ Line 412: [IPU1-0] 1.483560 s: I2C1: Error timeout 1 ms!!! [IPU1-0] 1.483621 s: [IPU1-0] Requires an UB964!!! Cannot stream out YUV422I (8 bit) [IPU1-0] 1.484109 s: Assertion @ Line: 623 in displayCtrlLink_drv.c: status == SYSTEM_LINK_STATUS_SOK : failed !!! [IPU1-0] 1.484597 s: Assertion @ Line: 623 in displayCtrlLink_drv.c: status == SYSTEM_LINK_STATUS_SOK : failed !!!