Part Number: TMS320C6678

Other Parts Discussed in Thread: SYSBIOS

Tool/software: Code Composer Studio

Hi

I'm testing PCIe interrupt for the PCIEXpress_Legacy_INTA.

MCSDK 2.1.2.6

CCS 8.3

Example project : C:\ti\pdk_C6678_1_1_2_6\packages\ti\drv\exampleProjects\PCIE_exampleProject

I added isr routine and setting(in cfg) in the PCIE_exampleProject

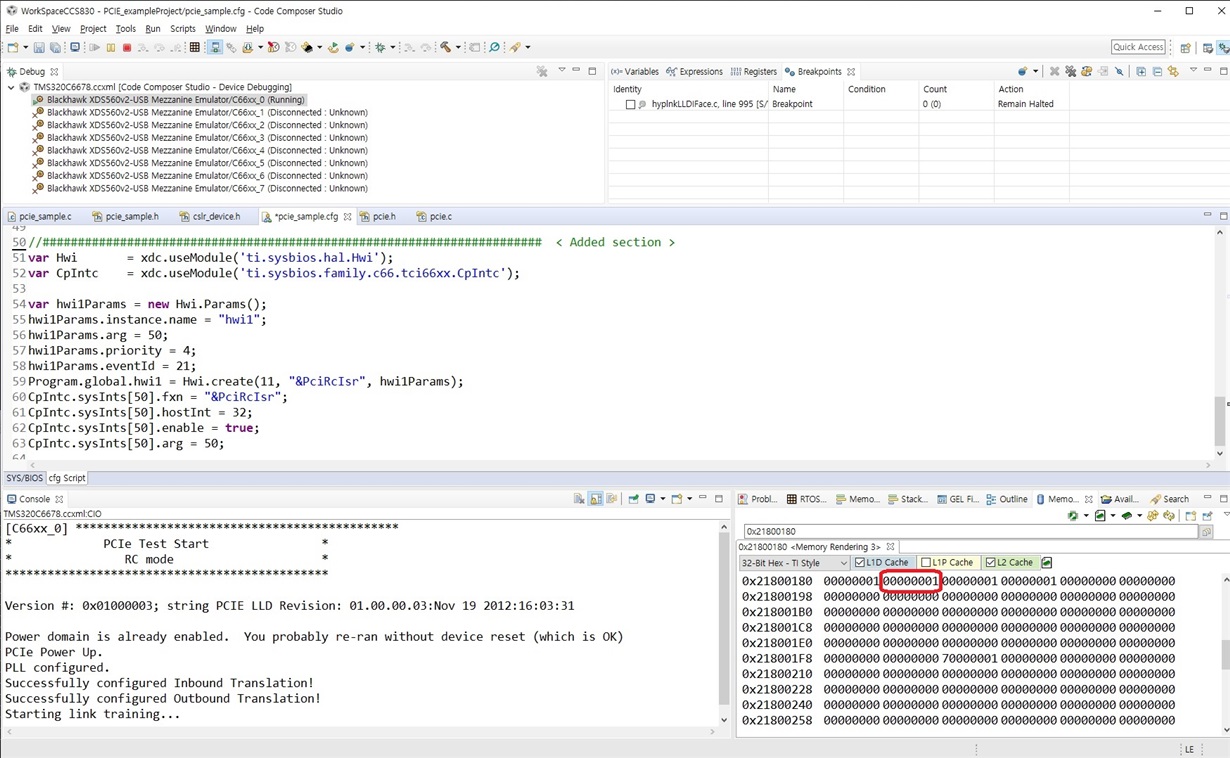

< Added cfg set-up and PCIe interrupt status(memory browser) >

As see abobe occure interrupt but not work ISR

The above experiment is intended to menual test incoming interrupts using RC mode in a PCIe example project with evmc6678.

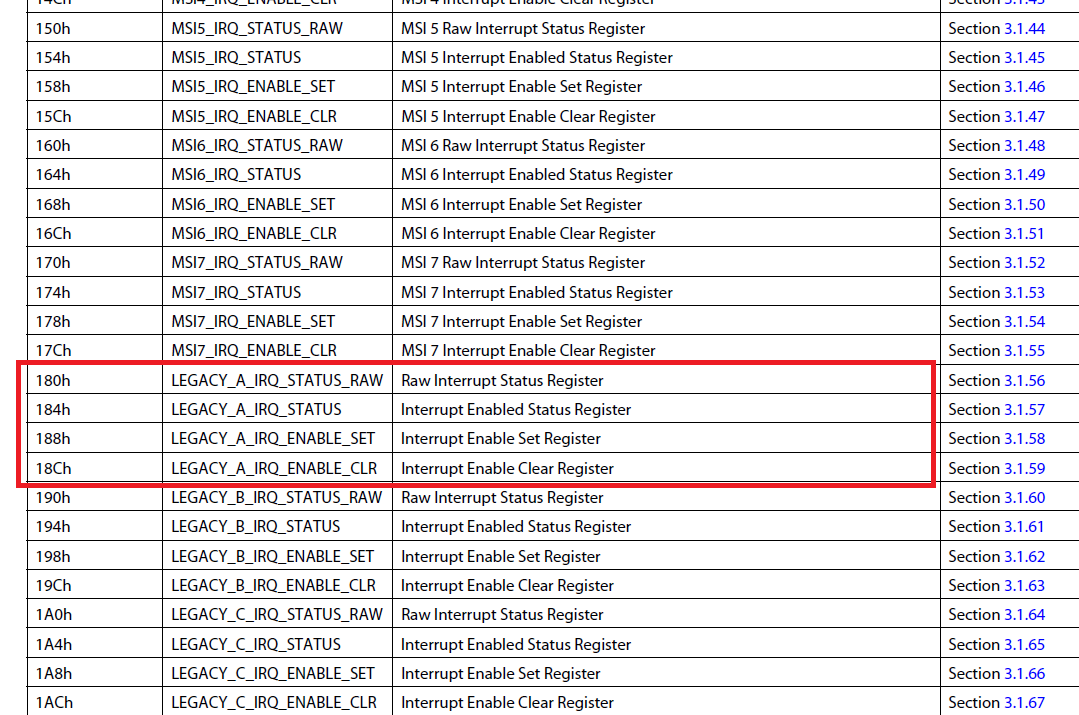

A manual interrupt was generated and tested using 1 in the Raw Interrupt Status Register (0x21800180).

In the example provided, the Interrupt Enabled Status Register shows that an interrupt has occurred.

However, they did not jump to ISR.

Need an other settings?