Tool/software: Linux

I need to configure timer5 as pwm function, modify the address according to other posts in the forum, run the program can reach a pwm waveform, but need to modify the period and duty cycle, try to modify the failure.

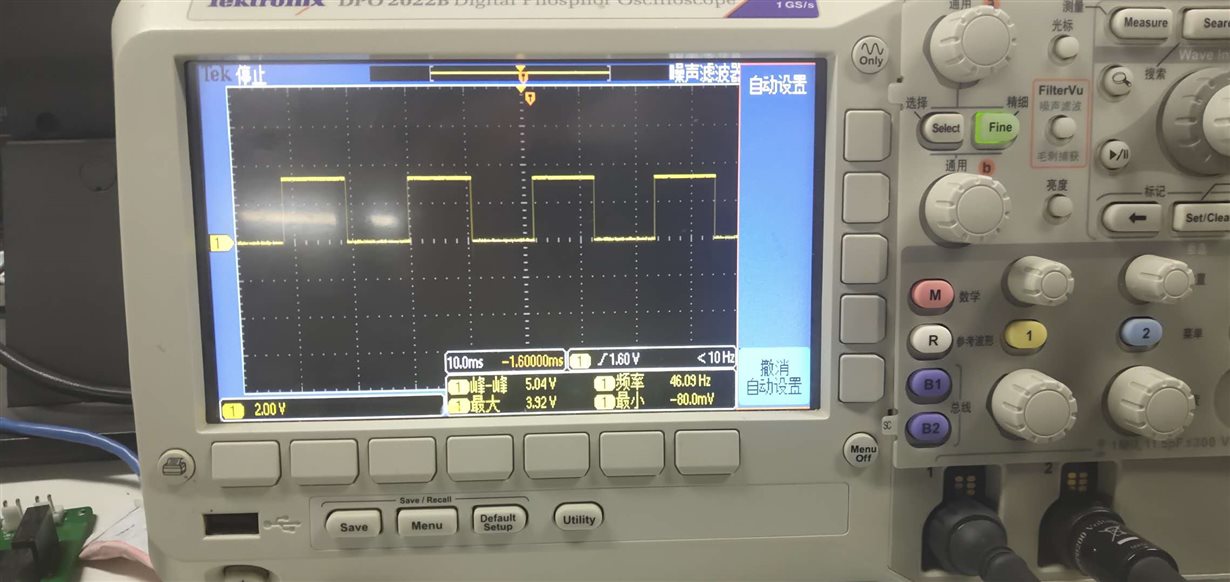

Changed to 2500us cycle, modified three places, but the test cycle is wrong

TLDR register value ffffffae

PRE 0 TCLR Register 48

Clock input of 32 kHz CLKSEL_TIMER5_CLK 0x02

Modify the case in a manual The register TLDR register value is changed to FFFF FFF0, the clock is originally selected 32kHZ, PRE=0, the period should be 500us, but the actual waveform period is not.

Below is the code is the implementation of the test example

#!/bin/sh

echo "Configuring Timer 5...\n"

#Select TIMER5 CLOCK SOURCE CLKSEL_TIMER5_CLK

devmem2 0x44E00518 w 0x2

#Enable timer to access its ctrl regs CM_PER_TIMER5_CLKCTRL

devmem2 0x44e000ec w 0x2

# Timer configurations.. Stop Timer. TCLR Register

# Auto-Reload

# Compare Mode Enabled

# Trigger set on overflow

# Toggle Mode

devmem2 0x48046038 w 0x48

# Set the re-load value

devmem2 0x48046040 w 0xFFFFFD39

# Setting a duty cycle to 50.7% TMAR Register

devmem2 0x4804604c w 0xFFFFFE9C

#set trigger TLDR Register

devmem2 0x48046044 w 0xFFFFFFF0

# Force the Timer to Smart-Idle TIOCP_CFG Register

devmem2 0x48046010 w 0x8

# Start Timer TCLR Register

devmem2 0x48046038 w 0x184B

# Verify that the timer is running,

# by polling the count register a

# few times. We should we up counting.

for i in {1..2}

do

echo "Timer Value $i"

devmem2 0x4804603C TCRR Register

# End

echo "Timer is Running!"

echo ""

echo "See J9 21 on the EVM" GPIO2_5-------TIMER5

echo ""

# Delay added to allow time for the first timer

# overflow to occur, before any consecutive memory

# accesses are made. (Just for standby testing).

sleep 1000

done

# Disable MODULEMODE of CM_PER_TIMER4_CLKCTRL register

# Only if this value is 0, are we able to wake-up from standby??

devmem2 0x44e000ec w 0x0

#END

I want you to help me see where there is a problem?

# Setting a duty cycle to 50.7% TMAR Register

devmem2 0x4804604c w 0xFFFFFE9C

In addition, I want to know how to calculate the duty cycle configuration.?

Thank you!!