I have a custom board with the AM1808. I'm trying to flash the board using UART2. My BOOTME message is coming out way too fast on reset. It's 2.31 Mbps instead of 115.2 Kbps.

From the Boot loader document sprab41c.pdf I learned that the UART divider is by default 8 and the UART oversampling 13. So normally you get

BAUD = 24MHz/(2 x 13 x 8) = 115384.

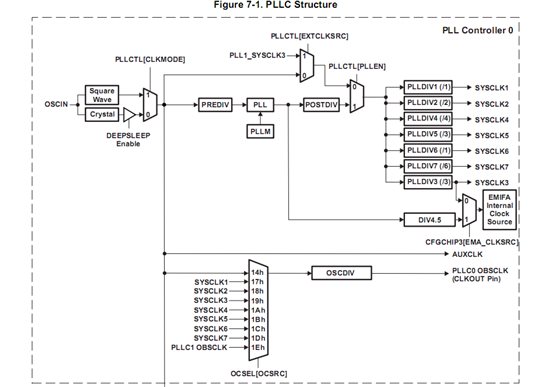

However, the default PLLM is 13h which would give a system frequency of 24MHz x 20 = 480 MHz. But it's supposed to be turned off after reset.

However using this value the BAUD would be calculated as:

BAUD = 480 MHz/(2 x 13 x 8) = 2.308 MHz which is what I'm getting. So it appears my PLL is getting enabled on reset. This agrees with the value I used in the UBL to get the correct baud rate there under emulator control. I used the /16 and DLL = 130 to get 480 MHz/(2*16*130) = 115384. But I had to comment out the line of code that (supposedly) takes it out of bypass mode since it causes the emulator to crash.

My question is: Is it possible by some pin set up to enable the PLL on reset? What else could be causing it to be on after reset? I have a reset button and even after power is good the same thing occurs on reset. Power sequencing looks good. I can run good from the emulator but cannot program the PLL under emulator control otherwise it crashes.

Help!