Other Parts Discussed in Thread: SYSBIOS, , AM5708, TMS320C6678

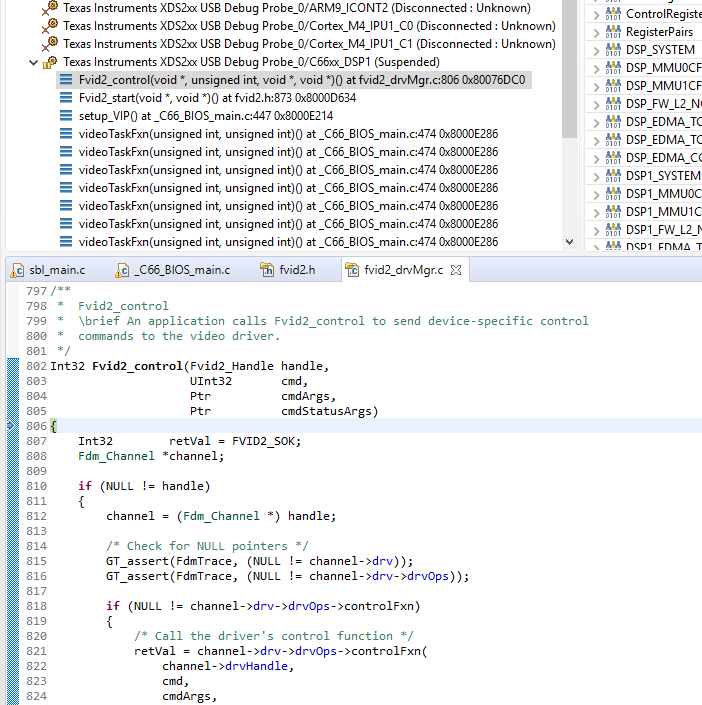

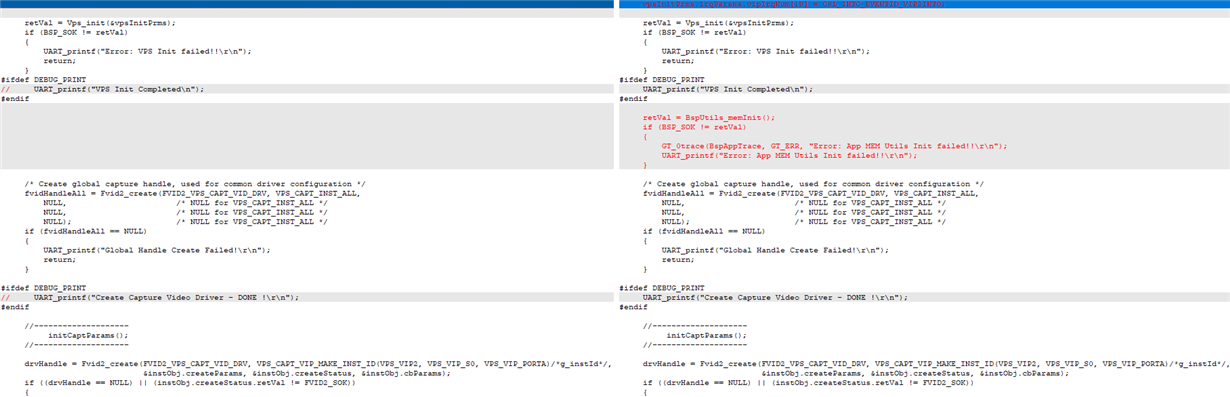

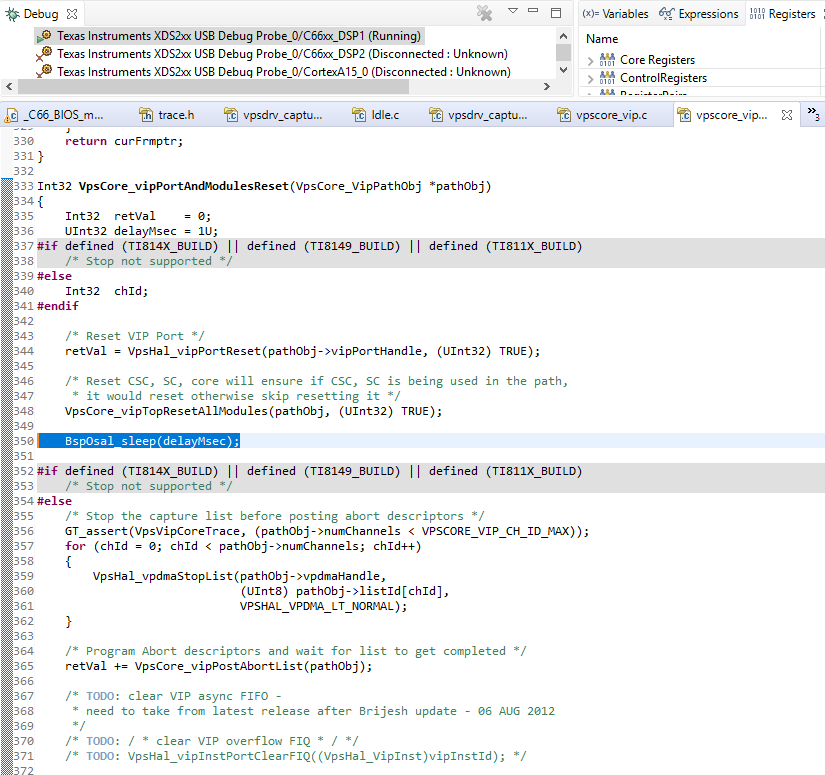

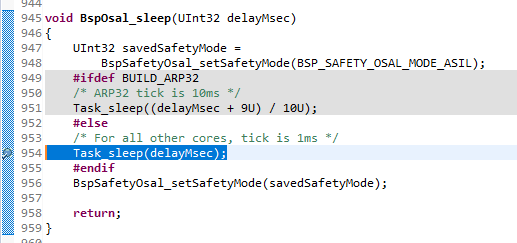

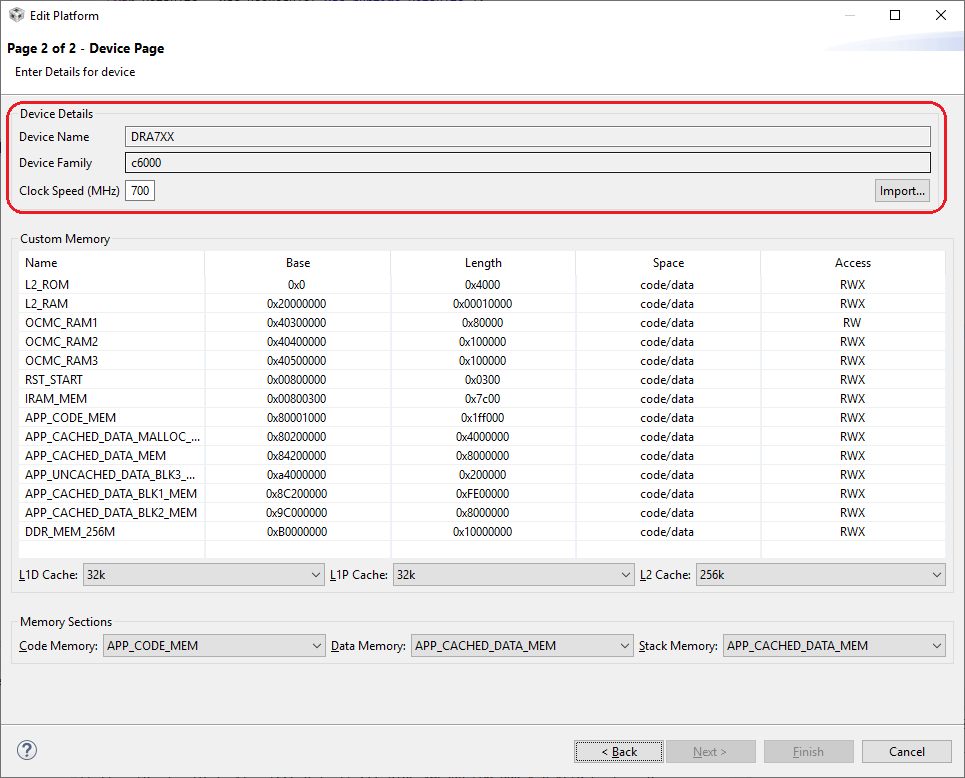

My project uses VIP on board AM572X EWM. After power on from SD card A15 boots MLO. Then MLO starts C66 which configurates FVID2 drivers. When I start C66 in baremetal FVID2 works. But when I start C66 under RTOS FVID2 stops on the FVID2_start(). The problem is like https://e2e.ti.com/support/processors/f/791/t/783033?RTOS-AM5728-boot-from-sd-card-and-the-app-stopped-at-Fvid2-start-. The update of PDK to the version of 1_0_15 didn't do any results. What is the solution of this problem? Please help me!