Other Parts Discussed in Thread: LM10011, LM21215

In one of the C6678 based board we delivered to customer, we are facing a peculiar issue as described below,

Smart Reflex is disabled [VID is disabled]

- Application is running in 8 different cores (8 different .out files), the same application is been tested in multiple other boards and it runs stable

- Boot-loader loads Core#0 application, then Core#0 application will kick-start and run cores#1-7

- In this one particular board, whenever core#4 comes-up; the Processor is hanged and all the other cores stop running.

- For experiment, we tried with different core clock frequency (from 100MHz to 1GHz),

- All 8 cores are running stable for core clock frequency 100MHz to 850MHz

- Beyond 850 MHz, core#4 issue is observed

- When we try running remaining 7 cores (except core#4), all 7 cores are running stable even for 1GHz core clock

- When we try running only core#0 and core#4 (only 2 cores), again the same issue is observed i.e. it is stable only upto 850MHz and beyond that processor is hanged.

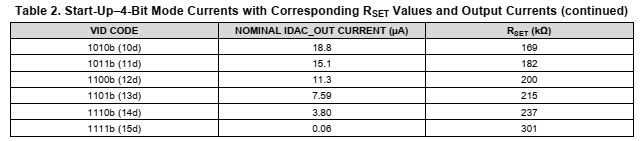

As ,mentioned above, we have disabled the VID, because if we enable it, Core#0 itself is not able to boot up.

May I know SRVnom for the device ?

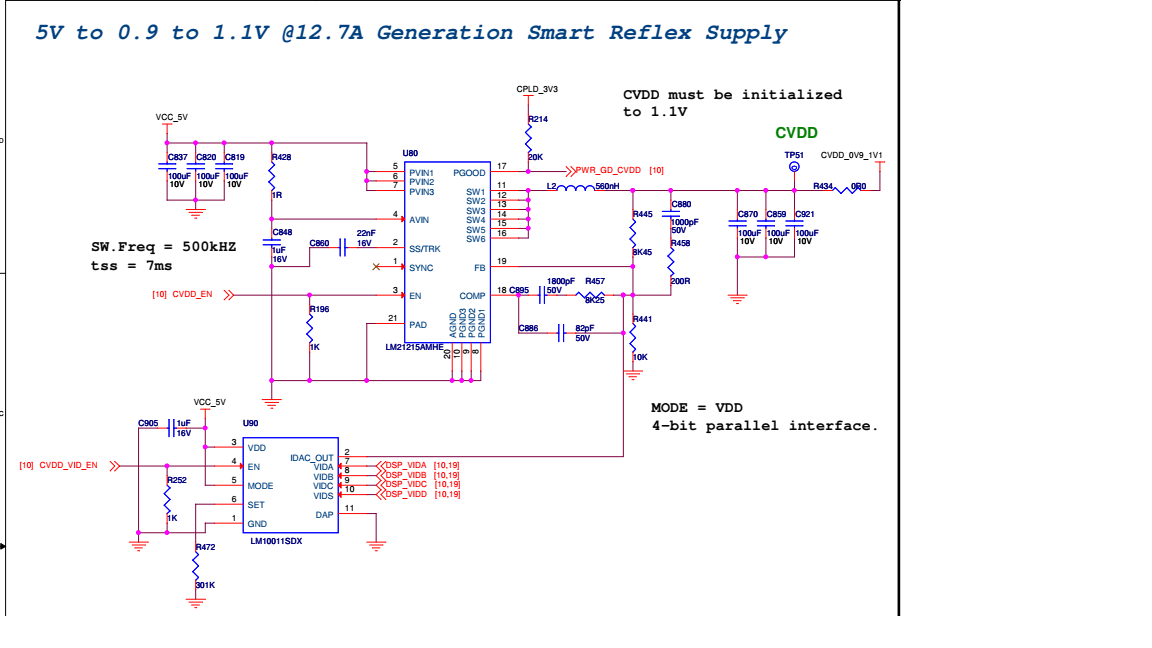

PS: Attaching the smart reflex circuitry.