Tool/software: Code Composer Studio

Hi.

We develop and use boards with TMS320C6678.

However, there was a problem with board modification due to discontinuation of NAND flash.

Previous NAND flash used NAND512R3A2SZA6E and now used MT29F1G08ABCHC on the board.

The development environment is as follows.

MCSDK 2.1.2.6

PDK 1.1.2.6

CCS 8.3

NAND flash device was changed, NANDWriter and platform_lib were modified, write and read was successful.

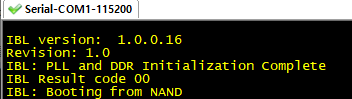

However, it does not become a NAND boot using the IBL that was previously used.

If the NAND flash device is changed, is there anything to be modified in the IBL?

Give me some advice.